# Prototyping with SpW in Japan

Osaka University/JAXA

M. Nomachi

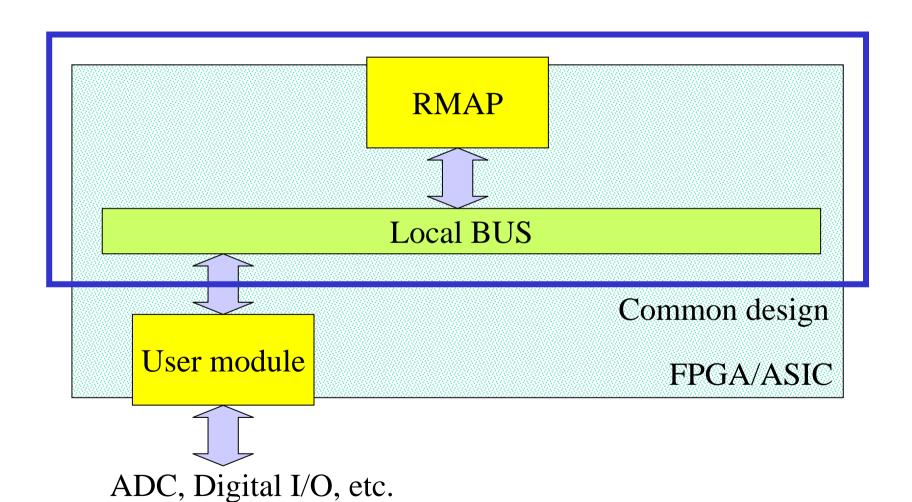

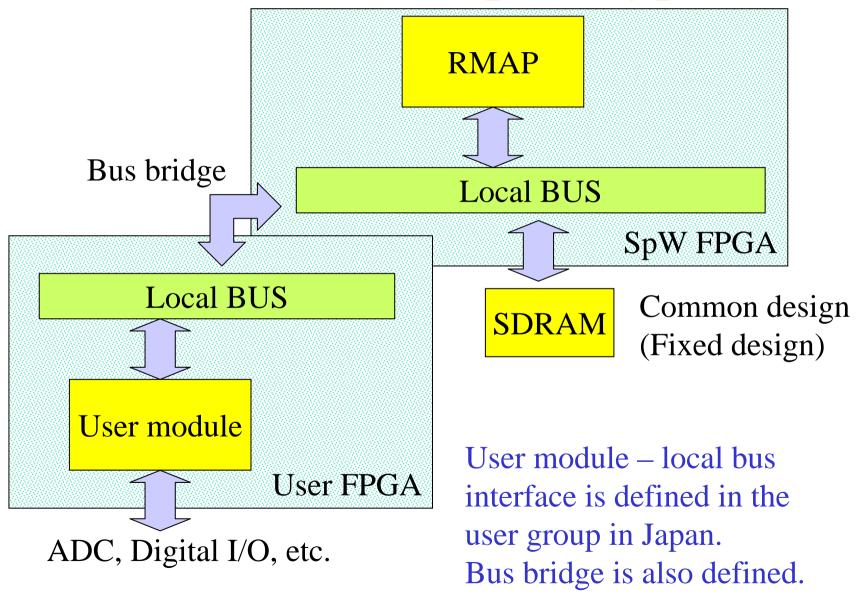

### Front-end module

# Front-end module prototype

### Data collection

Simple BUS

Collect data fragments

BUS with arbitration is defined

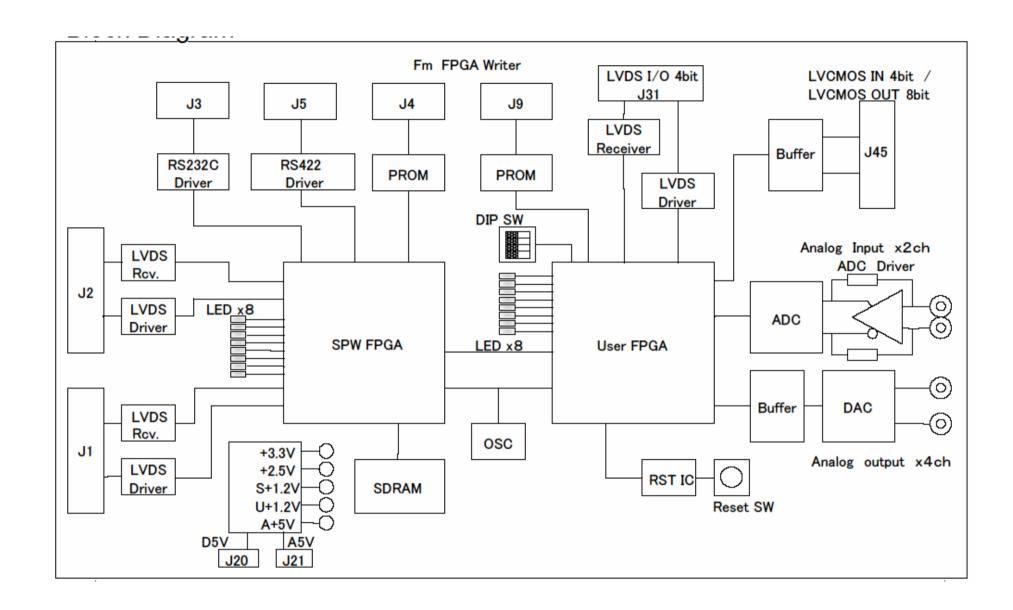

## SpW ADC/DAC BOARD

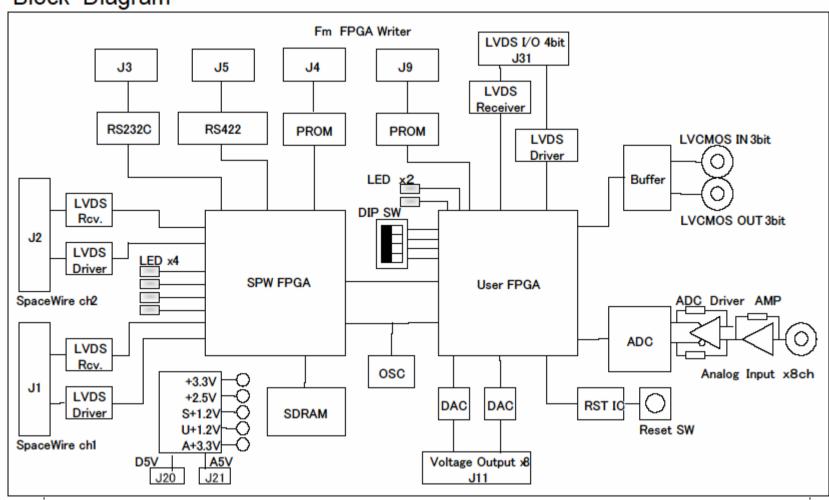

#### **ADC/DAC Board specified for Space Wire**

Connected to SpaceCube

Includes user FPGA and SDRAM and as external I/O, LVDS input/output,

LVCMOS input/output, serial I/F, AD converter and DA converter.

Joint development with JAXA (Japan Aerospace Exploration Agency)

| ITEMS           | SPECIFICATIONS                                                                                                                                                                                                                                |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SpW I/F         | 2ch installed in FPGA                                                                                                                                                                                                                         |

| External<br>I/F | Pararrel:LVCMOS IN 4bit OUT 8bit LVDS IN 4bit OUT 4bit Serial:RS232C 1ch RS422 1ch ADC:AD7688BRM Input:2ch ,Resolution:16bit Sample Rate:500 KSPS DAC:AD5544 ARS Resolution:16bit, Error:±1LSB Output voltage/Current range: 0~4.0V/2.5~1.5mA |

| Others          | SDRAM: x8bit 16MB<br>User logic:FPGA                                                                                                                                                                                                          |

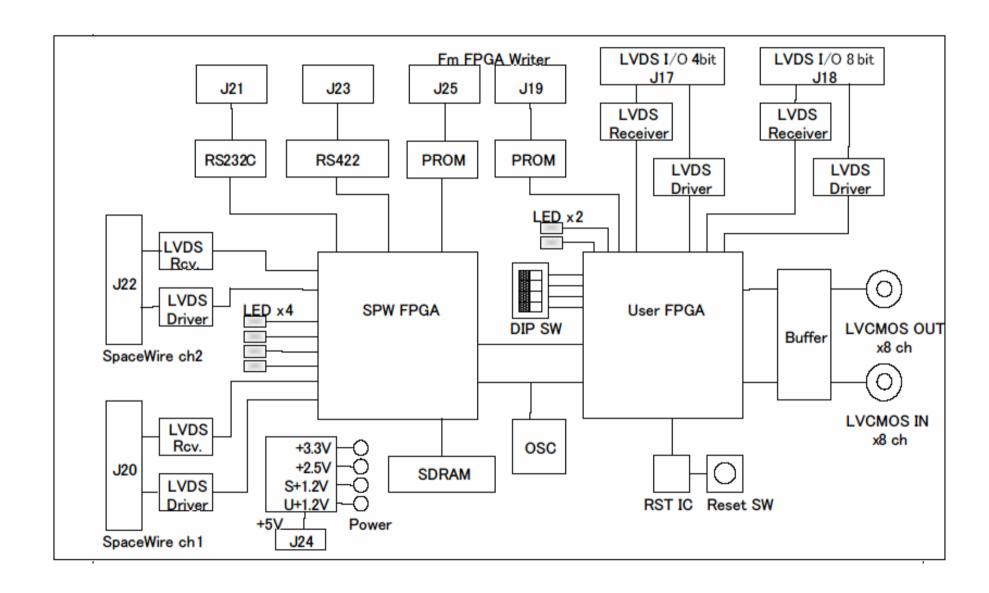

# SpW Digital I/O BOARD

#### Digital I/O Board specified for Space Wire

Connected to Space Cube

Includes user FPGA and SDRAM and as external I/O , LVDS input/output , LVCMOS input/output and serial I/F

Joint Development with JAXA (Japan Aerospace Exploration Agency)

| ITEMS           | SPECIFICATIONS                                                                                   |

|-----------------|--------------------------------------------------------------------------------------------------|

| SpW I/F         | 2ch are installed in the FPGA                                                                    |

| External<br>I/F | Pararrel:LVCMOS IN 8bit LVCMOS OUT 8bit LVDS IN 12bit LVDS OUT 12bit Serial:RS232C 1ch RS422 1ch |

| Others          | SDRAM: 16Mbyte<br>User logic: FPGA                                                               |

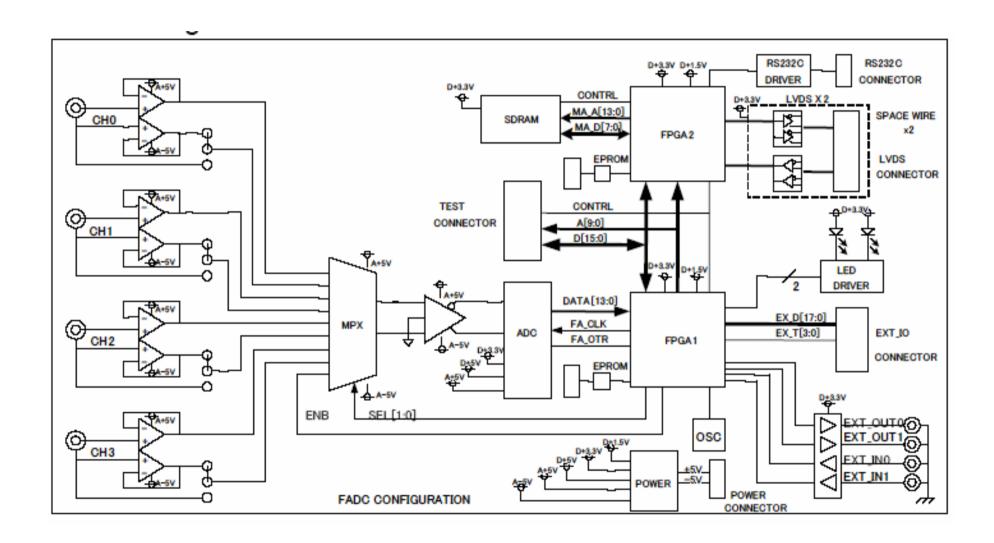

### FADC BOARD High Reso. SHIMAFUJI

#### Flash ADC Board specified for Space Wire

Connected to Space Cube

Analog input x 4ch, external I/O 26 bit

Joint development with JAXA (Japan Aerospace Exploration Agency)

| ITEMS               | SPECIFICATIONS                                                                              |

|---------------------|---------------------------------------------------------------------------------------------|

| Space Wire          | Installed in FPGA                                                                           |

| Analog<br>Input     | ADC:AD9240AS<br>Resolution:14bit<br>Conversion speed:100ns                                  |

| External<br>I/O     | Directly connected to FPGA:22bit (IN/OUT) Output via buffer:2bit Input via buffer:2bit      |

| Monitor<br>Function | Connectors for testing: Addressx10bit  Dataxx16bit  Serial: RS232C (Only Transmission data) |

### VATA-FADC Attachment SHIMAFUJI

#### Used with connection to FADC Board High Reso.

Analog outputx6ch, Analog inputx1ch and external I/O 12 bit Joint development with JAXA(Japan Aerospace Exploration Agency)

| ITEMS    | SPECIFICATIONS                                        |

|----------|-------------------------------------------------------|

| Analog   | Triple wires' serial DAC:LTC1446IS8 Resolution: 12bit |

| Output   | DNL errors at Maximum: 0.5 LSB                        |

|          | Conversion: 80ns<br>8bit pararrel DAC: CA33338AMZ     |

|          | DNL error at maximum: 1.0LSB                          |

|          | Conversion speed: 20ns                                |

| External | LVDS output:4bit                                      |

| 1/0      | Isolation output:7bit<br>Input:1bit                   |

| ., 0     | anjour.                                               |

### SpW Sampling ADC BOARD

#### Sampling ADC Board specified for Space Wire

Connected to Space Cube

Includes user FPGA and SDRAM and as external I/O, LVDS input/output, LVCMOS input/output, serial I/F and AD Converter

Joint Development with JAXA(Japan Aerospace Exploration Agency)

| ITEMS           | SPECIFICATIONS                                                                                                                                                                                                             |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SpW I/F         | 2ch are installed in the FPGA                                                                                                                                                                                              |

| External<br>I/F | Pararrel:LVCMOS IN/OUT 3bit LVDS IN/OUT 4bitt Serial:RS232C 1ch RS422 1ch ADC:ADS5721IPFP Input: 8ch, Resolution:12bit Sample Rate:50MSPS DAC:AD5324ARM Resolution:12bit, Error:±4LSB OutputVoltage range:2.5~5.5v/200 μ A |

| Others          | SDRAM:16Mbyte<br>User logic: FPGA                                                                                                                                                                                          |

DIOUN DIUGIUIII

SHIMAFUJI Electric Inc. = 144-0051 KC Bldg. 5F, 8-1-15, Nishikamata, Ota-ku, Tokyo, Japan

TEL: 03-3733-8308 FAX: 03-3733-8318 E-mail: info@shimafuji.co.jp URL: http://www.shimafuji.co.jp/

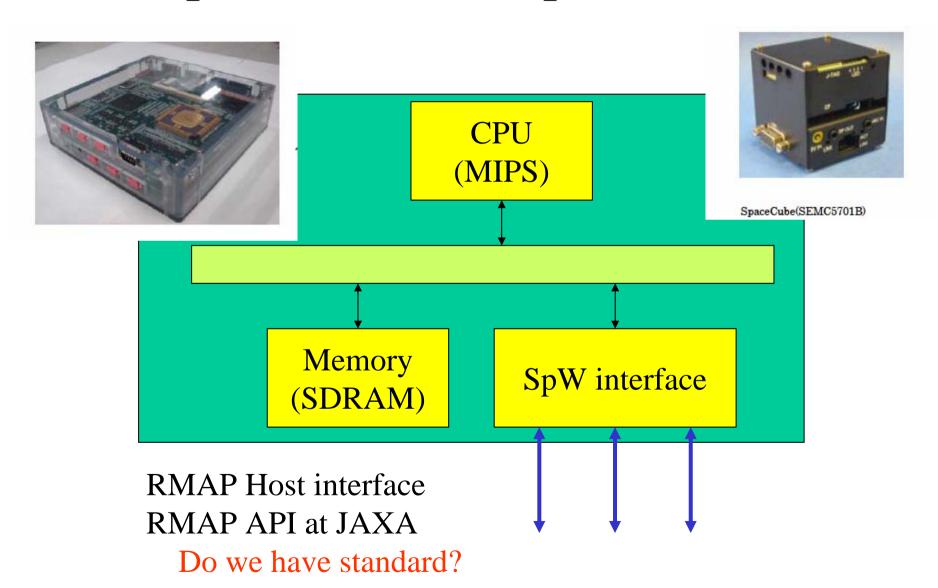

# RMAP master (Space Cube and Space Cube II)

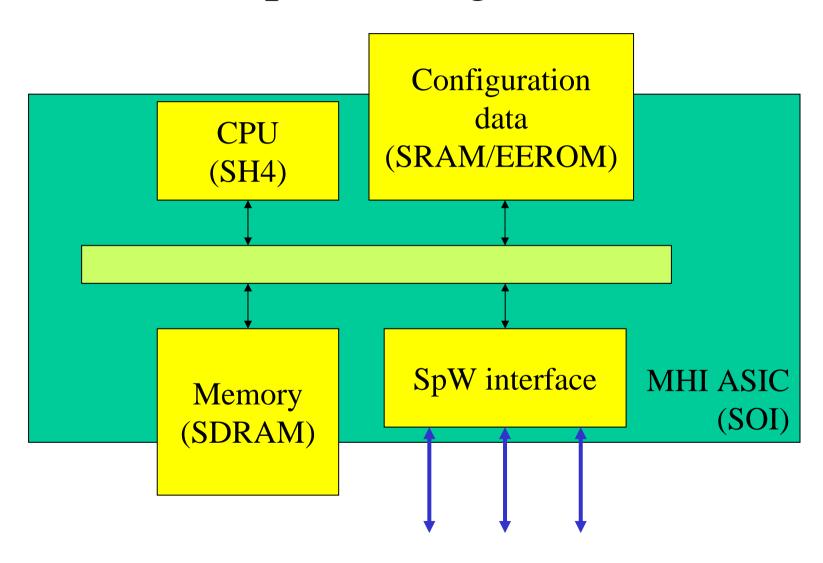

# RMAP master (Data processing Unit)

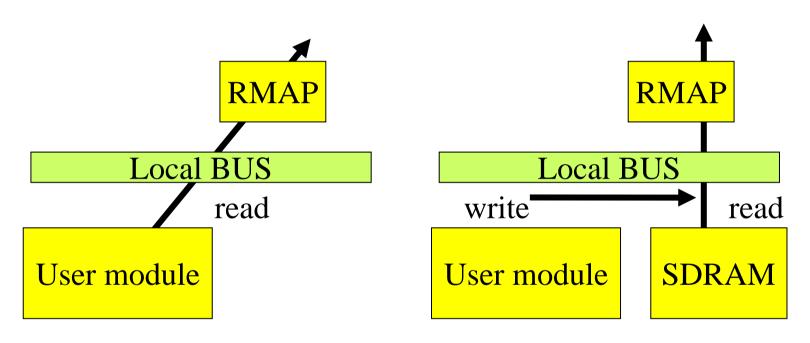

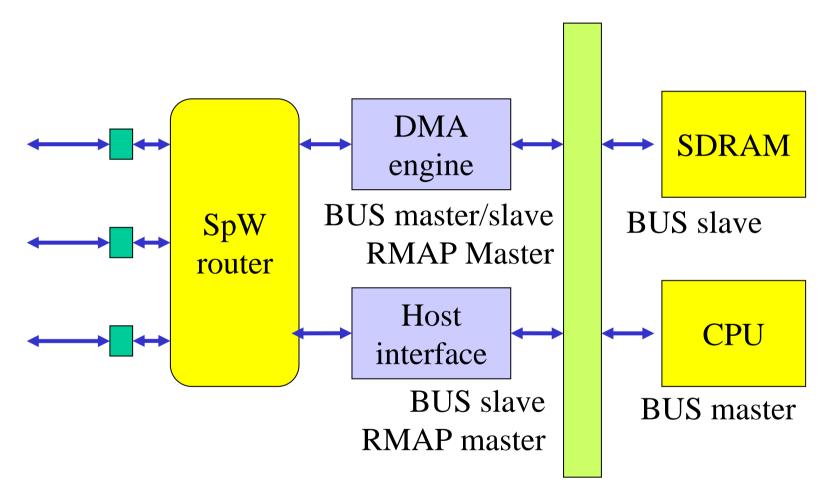

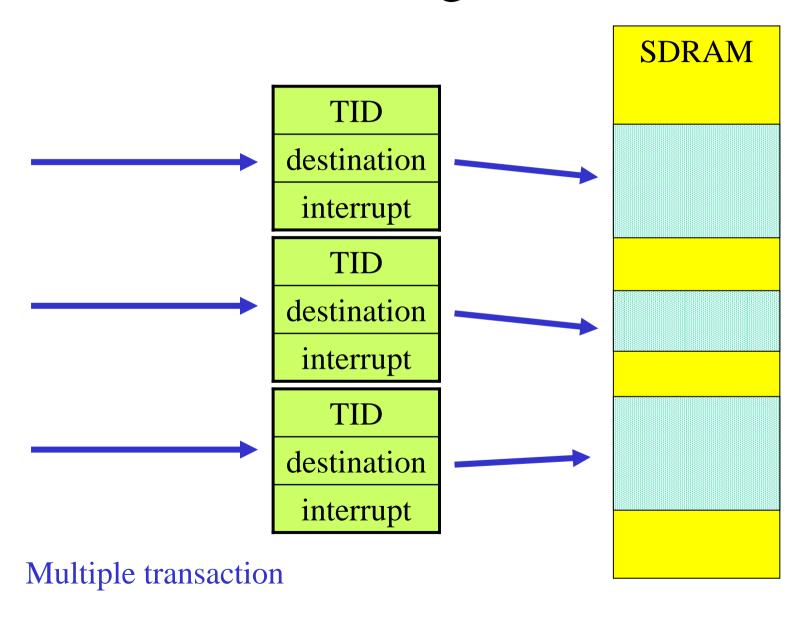

### DMA transfer

Will be implemented in MHI ASIC DMA engine and Host interface may share one router port.

# DMA engine

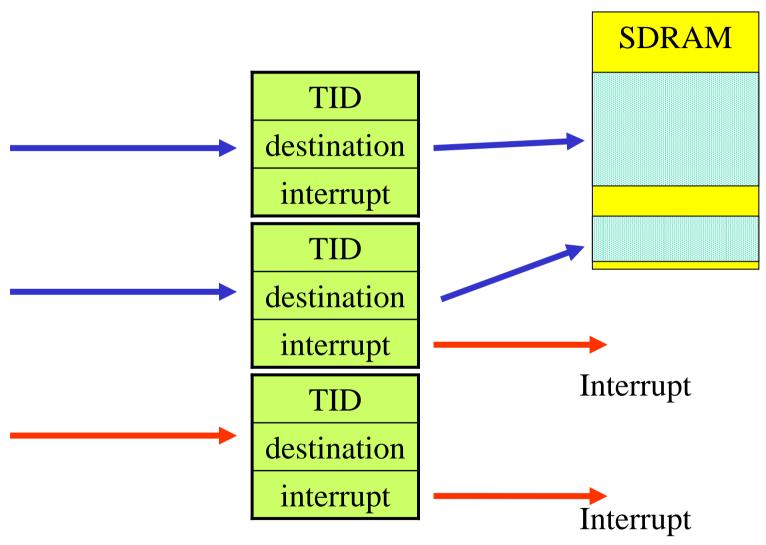

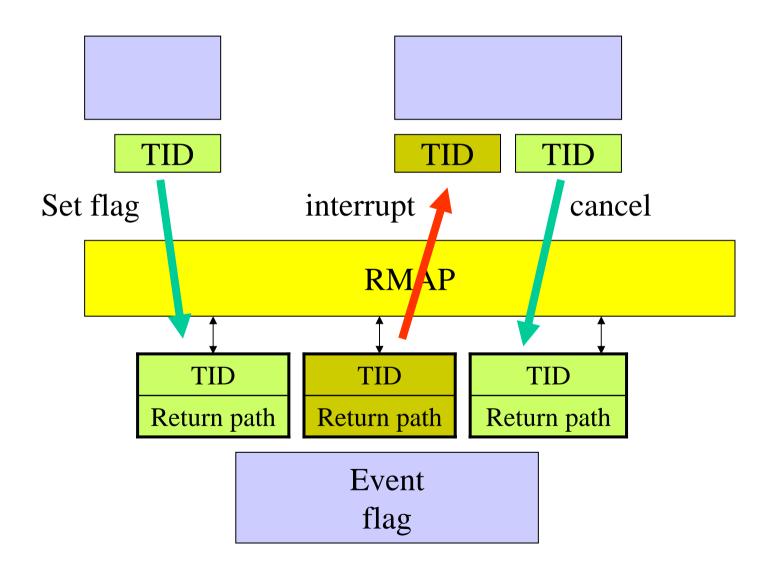

## Interrupt handling

Multiple transaction

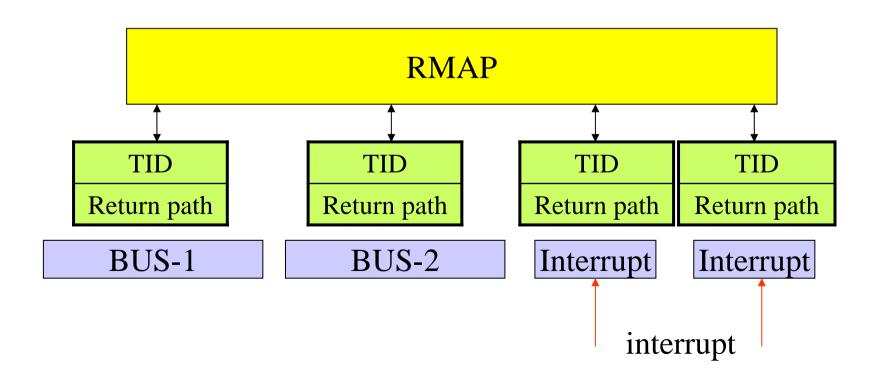

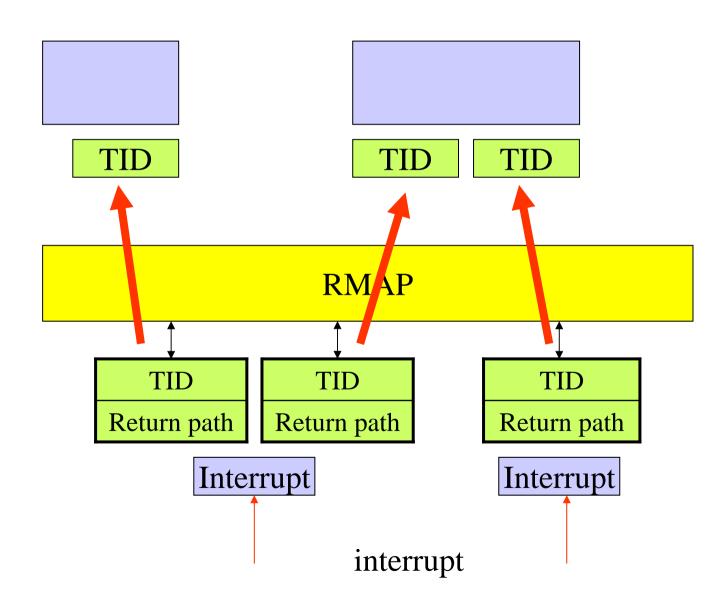

# Multiple transaction handling at a front-end module

### Multiple bus

High speed one direction bus/random access bus Interrupt handling

## Interrupt handling

### Event flag for multi processing units

### summary

- Common architecture for many applications

- Various data collection scheme

- Direct access

- Collection of fragmented data

- DMA engine

- Multi transaction

- Interrupt with RMAP

- Evaluation modules and templates

- Increase the number of companies

- More and more active students

- Real Time Conference 2007 at Chicago 29/4-5/5

- IEEE nuclear/particle and plasma physics

- Space applications are welcome