ADSANTEC

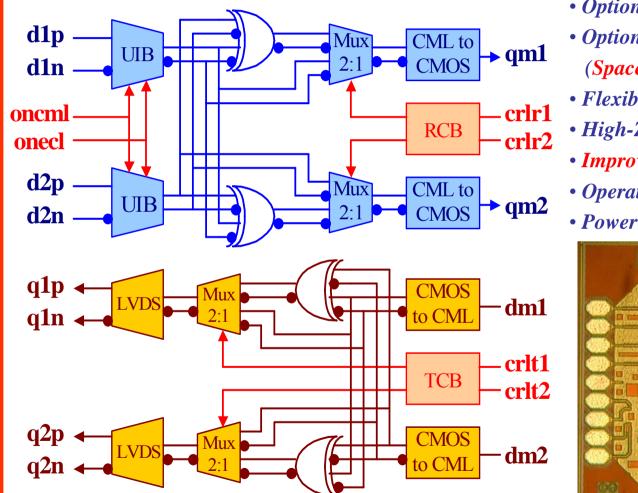

# **Dual CMOS/LVDS Converter**

- Optional CML/ECL input modes;

- Optional DS encoding/decoding (Space Wire compatibility);

- Flexible operational modes;

- High-Z output disabled states;

- Improved TID Protection (RHBT);

- Operational Speed 0...2Gb/s;

ADSANTEC

• Based on SiGe HBTs;

• Fully compliant with IEEE Std. 1596.3-1996 and ANSI/TIA/EIA-644-1995.

• Improved TID protection (by-technology);

• Low power consumption.

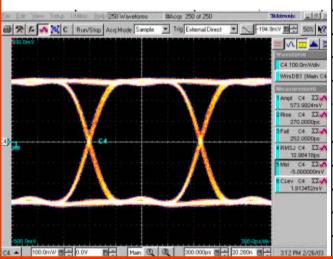

|                                                       | Symbol                                                                          | Parameter                                                              | Min      |          |       | Max         |            |             | Units |

|-------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------|----------|----------|-------|-------------|------------|-------------|-------|

|                                                       | Symoor                                                                          |                                                                        | Standard | Simul.   | Meas. | Meas.       | Simul.     | Standard    |       |

|                                                       | $V_{CC}$                                                                        | Main supply voltage                                                    |          | 3.1      | 3.1   | 3.5         | 3.5        |             | V     |

|                                                       | V <sub>CC_LVDS</sub>                                                            | OD supply voltage                                                      |          | 1.7      | 1.7   | 3.5         | 3.5        |             | V     |

| nd                                                    | $ V_{dif} $                                                                     | Output differential voltage                                            | 250      | 280      | 265   | 300         | 360        | 400         | mV    |

| <i>iu</i>                                             | $V_{osDC}$                                                                      | DC output offset voltage                                               | 1125     | 1182     | 1192  | 1200        | 1233       | 1275        | mV    |

|                                                       | $V_{osHS}$                                                                      | Output offset voltage at f <sub>max</sub>                              | 1125     | 1133     | 1146  | 1153        | 1198       | 1275        | mV    |

| 2                                                     | V <sub>hi</sub> -V <sub>lo</sub>                                                | Output voltage shift (DC impedance<br>test)                            | 178      | 193      | 255   | 262         | 280        | 295         | mV    |

|                                                       | R <sub>o</sub>                                                                  | DC output impedance (derived from<br>V <sub>h</sub> -V <sub>lo</sub> ) | 40       | 47       | 88    | 95          | 117        | 140         | Ω     |

| •                                                     | $egin{aligned} &  (V_{ahn}^- & V_{alo})^- & (V_{bhn}^- V_{blo})  \end{aligned}$ | Mismatch of the output voltage shifts<br>(output impedance deviation)  | -        | -        | -     | 9<br>(4.5%) | 12<br>(6%) | 20<br>(10%) | mV    |

| 50% 1                                                 | Zo                                                                              | AC output impedance (from 0 to $f_{max}$ )                             | 40       | 43       | 52    | -           | 123        | 140         | Ω     |

|                                                       | I <sub>totalD</sub>                                                             | Total current (1 data buffer) at 1Gb/s                                 | -        | 4.1      | 4.4   | 5.2         | 5.6        | -           | mA    |

| 00:0m¥/div<br>0B1 (Main C4                            | I <sub>total C</sub>                                                            | Total current (1 clock buffer) at 1GHz                                 | -        | 5.6      | 6.0   | 6.4         | 6.9        | -           | mA    |

|                                                       | IsgND                                                                           | Output current, driver shorted to GND                                  | -        | <u>-</u> | 21    | 22          | 16.5       | 40          | mА    |

| 73.9924mV<br>C4 IX<br>70.0000ps<br>C4 IX<br>52.0000ps | I <sub>sab</sub>                                                                | Output current, outputs shorted<br>together                            | -        | -        | 5.4   | 5.6         | 6.5        | 12          | mA    |

| 2 964 18ps                                            | fmaxD                                                                           | Speed range (data buffer)                                              | -        | 0        | -     | 777.6       | 1.0        | ÷.          | Gb/s  |

| 04 XX<br>0000000mV<br>04 XX<br>913452mV               | fmaxC                                                                           | Frequency range (clock buffer)                                         | -        | 0        | 8     | 777.6       | 10         |             | GHz   |

| 010402011Y                                            | $t_{rD}/t_{fD}$                                                                 | Rise/fall time (data buffer, 20%-80%)                                  | 300      | -        | 370   | 400         | 402        | 500         | ps    |

|                                                       | t <sub>rC</sub> /t <sub>fC</sub>                                                | Rise/fall time (clock buffer, 20%-80%)                                 |          | -        | 210   | 230         | 280        |             | ps    |

| PM 2/26/03                                            | j                                                                               | Jitter (data buffer)                                                   | 2        | 9        | 13.5  | 14.2        | 14         | -           | ps    |

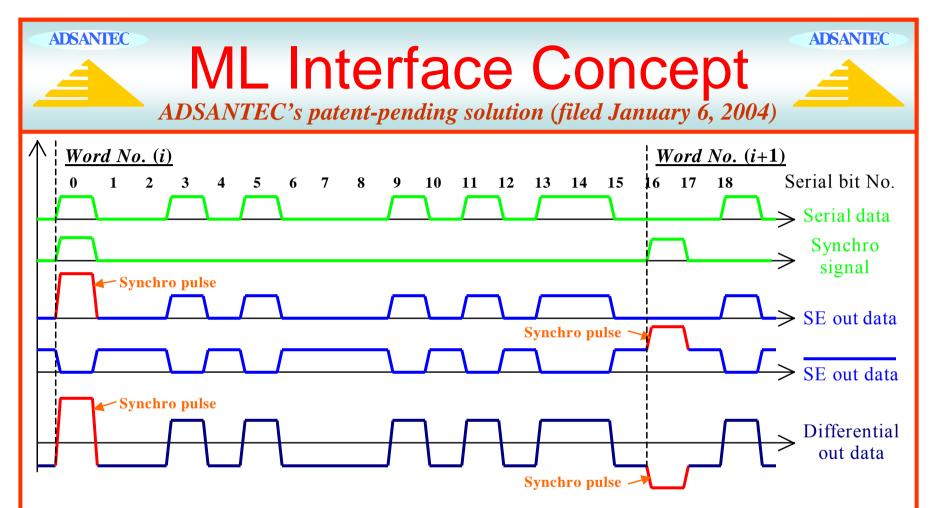

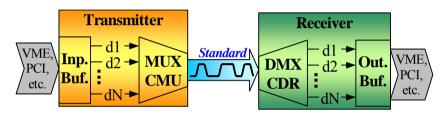

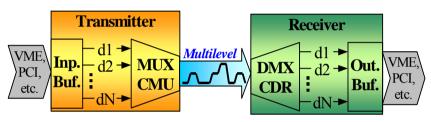

A *Synchro pulse* of increased amplitude is imposed by the *transmitter* onto the *first bit* of ever *outgoing serialzed word*.

The pulses appear *arbitrarily* in *single-ended* (SE) data, but *regularly* in *differential* data.

The repeating pulses are *retrieved* from the *incoming serial data stream* by the *receiver* and are used for simplified *clock & data recovery* and *bit/word alignment*.

# 2-Level vs. Multi-Level

ADSANTEC

ADSANTEC's patent-pending solution (filed January 6, 2004)

### **Standard Serial Interface**

#### Advantages:

ADSANIEC

- simple input/output circuitry,

- simple media loss equalization.

#### **Problems:** ٠

- reduced transmission speed,

- extra latency,

- complicated hardware,

- code-specific encoding software,

- poor upgrade ability.

### **Multilevel Interface**

- Advantages:

- maximum transmission speed,

- minimal latency,

- efficient clock recovery,

- easy multi-channel alignment,

- high upgrade ability.

#### • Problems:

- more complex I/O circuitry,

- more complicated equalization.

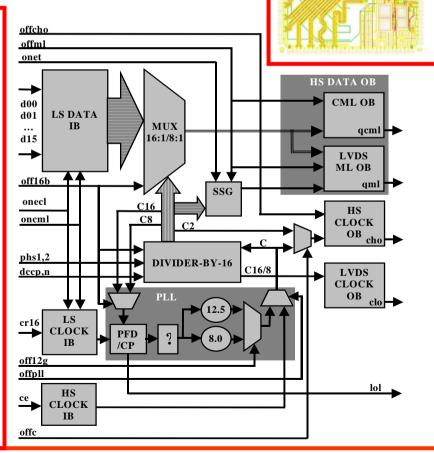

Multi-Level MUX CMU

## ADSANTEC

12.5/8.0*Gbps*, 16:1/8:1 Serializer with CMU or 12.5*Gbps* Digital broad-band 16:1 Serializer

•Single +3.3*V* power supply (V<sub>CC</sub>);

- LVDS, CML, and ECL compatible Input Data and Reference Clock buffers;

- Output Data buffer featuring LVDS Multi-level or CML output signaling;

- On-chip PLL provides clock synthesis from lowspeed clock reference;

- Selectable CML Clock Output buffer with a standard 50*Ohm* termination scheme;

- Full-rate CML Input Clock buffer with on-chip 50*Ohm* termination;

- Clock-Divided-By-Sixteen LVDS Output Buffer with 90°-step phase selection;

- Rated for industrial temperature range;

- 550mW nominal power consumption at 12.5Gbps.

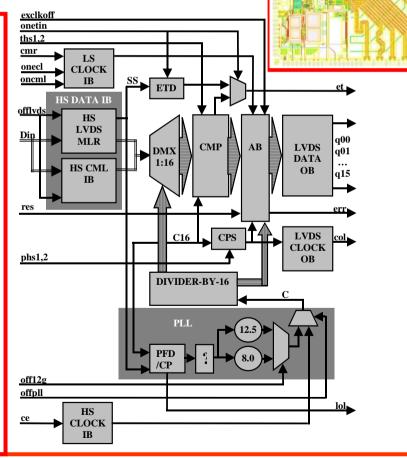

Multi-Level DMUX CMU

## 12.5/8.0*Gbps* 1:16 Deserializer with CMU or 12.5*Gbps* Digital broad-band 1:16 Deserializer

- Single +3.3*V* power supply (V<sub>CC</sub>);

- Input Data buffer featuring a selectable Multilevel LVDS or CML interface;

- LVDS Output Data and Clock buffers for low-power operation;

- On-chip PLL provides clock synthesis from recovered Synchro-pulses;

- Full-rate CML Input Clock buffer with on-chip 50*Ohm* termination;

- Output FIFO with external Master Clock input;

- Digital comparator with programmable threshold;

- Clock-Divided-By-Sixteen LVDS Output buffer with 90°-step phase selection;

- Rated for industrial temperature range;

- 450mW nominal power consumption at 12.5Gbps.

ADSANTEC

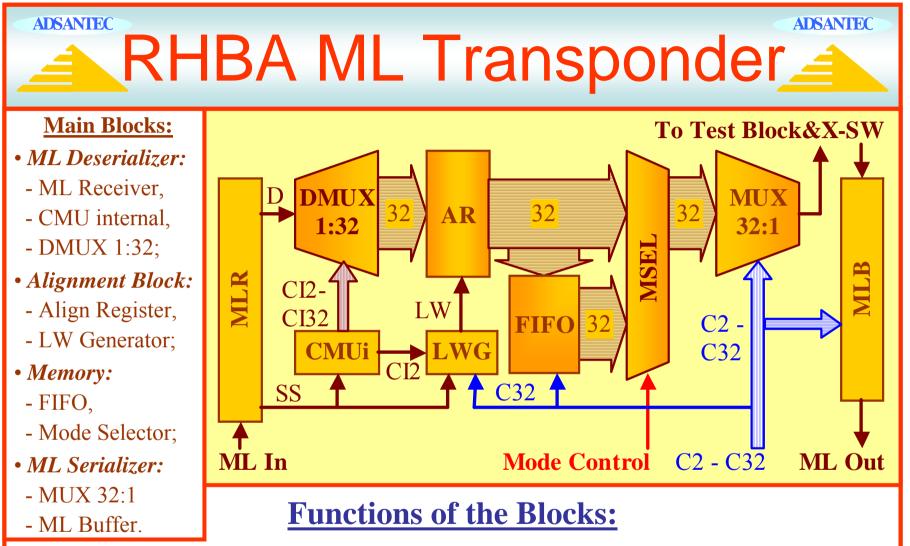

- <u>ML Deserializer</u> reconstructs clock signals and 32-bit parallel data from input serial bit stream;

- <u>Alignment Block</u> retimes the data by Local Write (LW) signal not coincident with I/O clocks;

- <u>Memory</u> stores the data temporarily and delivers either original or delayed data to the MUX;

- <u>ML Serializer</u> converts parallel data into serial bit stream with imposed Synchro pulses.

- Based on SiGe HBT CML cells;

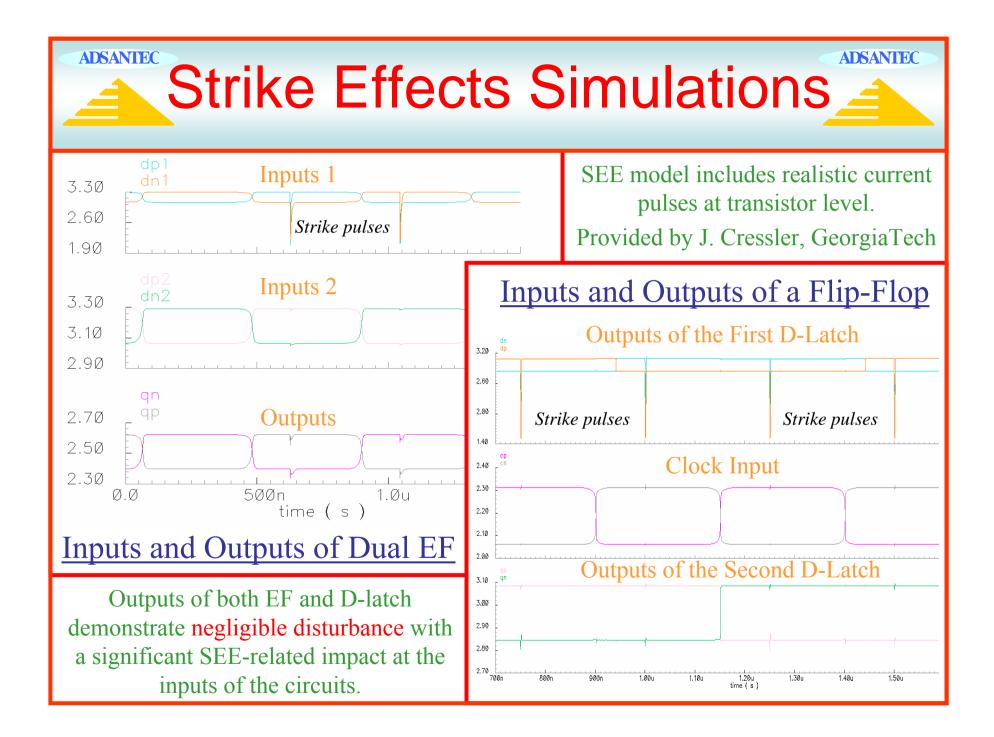

- Utilization of logic functions for SEE/SEU mitigation;

- Lower speed/power/area penalty than standard TMV technique;

- 6 power levels from 14µW/cell to 1.85mW/cell;

- Up to 2.5*Gb/s* worst-case simulated speed;

- Complete RHBA library of standard and custom cells including:

660MHz Ring VCO, PFD, and Charge Pump; I/Os, ML I/Os; D-Type Latch, DFFs, RSFFs Buffer and Emitter Follower; MUX2:1, AND, and XOR Gates.

#### ADSANIEC

ADSANIEC

# Summary / Conclusion

- A dual, low power CMOS-to-LVDS IC solution has been presented that operates at GHz speeds with an improved level of TID protection. The IC contains switchable Data Strobing encoding/decoding circuitry that is fully Space Wire compatible and innovative I/O blocks.

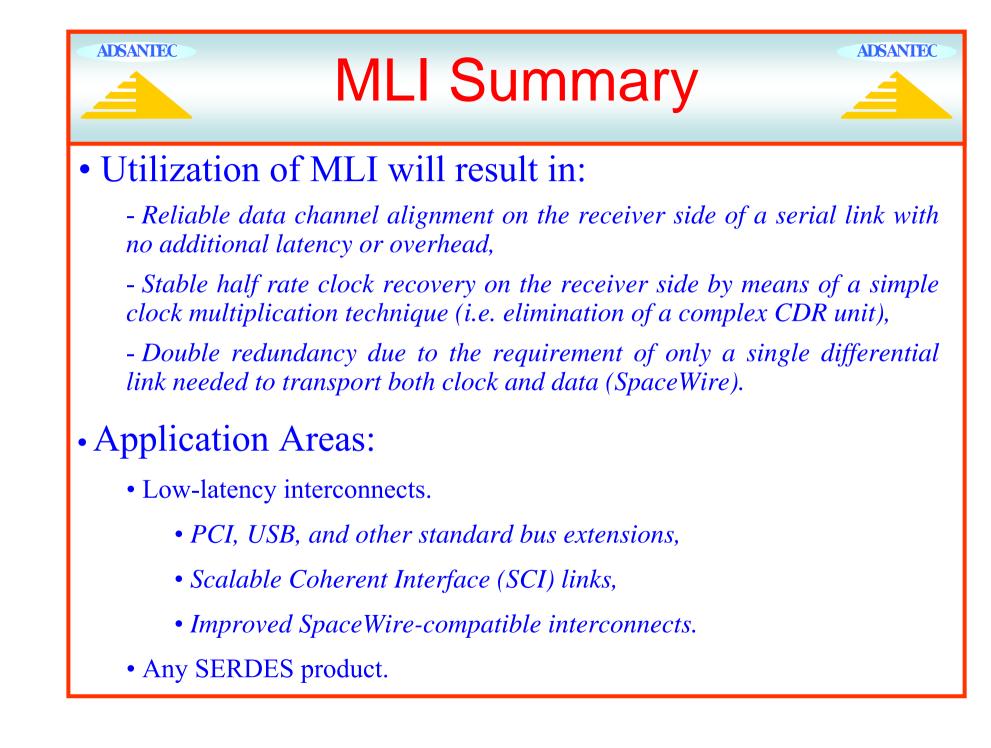

- ADSANTEC has developed a novel multilevel interface (MLI) technology that significantly improves the performance of high-speed serial data links, specifically Space Wire interconnects, and has multiple fields of application.

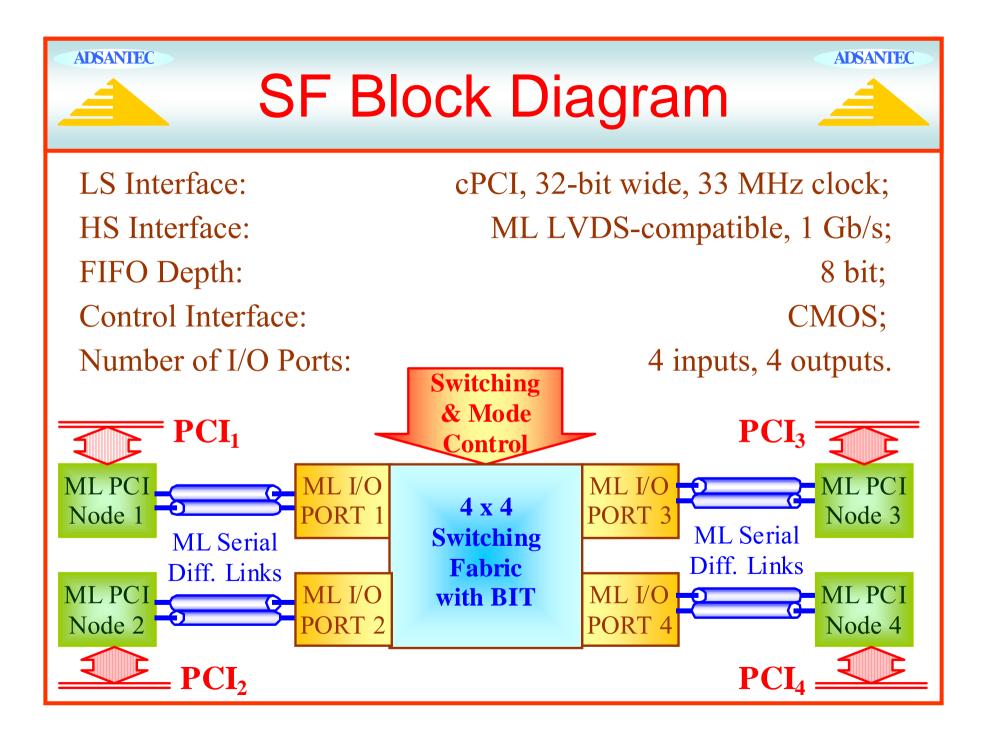

- An innovative radiation hard by architecture (RHBA) library has been utilized to construct a ML transponder that is utilized in the presented switch fabric intended for cPCI bus extension.