Ref.:UoD\_SpW-10X\_DataSheetIssue:2.0Date:18<sup>th</sup> August 2006

# SpaceWire Router

# **Data Sheet**

| Ref:           | UoD_SpW-10X_DataSheet                                                        |

|----------------|------------------------------------------------------------------------------|

| Document Revis | ion: Issue 2.0                                                               |

| Date:          | 18 <sup>th</sup> August 2006                                                 |

|                |                                                                              |

| Prepared by -  | Chris McClements, University of Dundee<br>Steve Parkes, University of Dundee |

| Checked by -   | Steve Parkes, University of Dundee                                           |

ESA Manager - Pierre Fabry, ESTEC

Ref.: UoD\_SpW-10X\_ DataSheet Issue: 2.0

Data-Sheet

Date: 18<sup>th</sup> August 2006

# Document Change log

| Date                          | Issue     | Comments                                                                                        | Author           |

|-------------------------------|-----------|-------------------------------------------------------------------------------------------------|------------------|

| 19 <sup>th</sup> -March-2004  | Issue 1.0 | Initial draft version                                                                           | Chris McClements |

|                               |           |                                                                                                 |                  |

| 26 <sup>th</sup> -August-2004 | Issue 1.2 | Timing for FPGA model added                                                                     | Chris McClements |

| 16 November 2004              | Issue 1.3 | Register Definitions Updated                                                                    | Chris McClements |

| 27 April 2004                 | Issue 1.4 | Latency and Jitter Specifications added                                                         | Chris McClements |

| 2 May 2005                    | Issue 1.5 | Footer indicates "Preliminary."<br>Section 8.6 subject to change<br>notice added to front page. | Steve Parkes     |

| 21 December 2005              | Issue 1.6 | RMAP section added                                                                              | Chris McClements |

| 19 <sup>th</sup> July 2006    | Issue 1.7 | Corrections and clarifications                                                                  | Chris McClements |

| 18 <sup>th</sup> August 2006  | Issue 2.0 | Editorial changes and<br>clarifications                                                         | Steve Parkes     |

# CONTENTS

| CONTENTS                                 | 3  |

|------------------------------------------|----|

| I LIST OF FIGURES                        | 7  |

| II LIST OF TABLES                        | 8  |

| 1. INTRODUCTION                          | 10 |

| 1.1 TERMS AND ACRONYMS                   | 10 |

| 1.2 DOCUMENTS                            | 10 |

| 2. APPLICATIONS                          | 12 |

| 2.1 STAND-ALONE ROUTER                   | 12 |

| 2.2 NODE INTERFACE                       | 12 |

| 2.3 EMBEDDED ROUTER                      | 12 |

| 2.4 EXPANDING THE NUMBER OF ROUTER PORTS | 12 |

| 3. FUNCTIONAL OVERVIEW                   | 13 |

| 3.1 SPACEWIRE PORTS                      | 14 |

| 3.2 EXTERNAL PORTS                       | 14 |

| 3.3 CONFIGURATION PORT                   | 15 |

| 3.4 ROUTING TABLE                        | 15 |

| 3.5 ROUTING CONTROL LOGIC AND CROSSBAR   | 15 |

| 3.6 TIME-CODE PROCESSING                 | 16 |

| 3.7 CONTROL/STATUS REGISTERS             | 16 |

| 4. DEVICE INTERFACE                      | 17 |

| 4.1 GLOBAL SIGNALS                       | 17 |

| 4.2 SPACEWIRE SIGNALS                    | 18 |

| 4.3 EXTERNAL PORT DATA SIGNALS           | 20 |

| 4.4 TIME-CODE SIGNALS                    | 22 |

| 4.5 LINK ERROR INDICATION SIGNALS        | 23 |

| 4.6 RESET CONFIGURATION SIGNALS          | 24 |

| Prelimary                                | 3  |

| 4.7 POWER AND GROUND SIGNALS                                           | 27 |

|------------------------------------------------------------------------|----|

| 5. INTERFACE OPERATIONS                                                | 28 |

| 5.1 EXTERNAL PORT INTERFACE OPERATION                                  | 28 |

| 5.2 TIME-CODE INTERFACE OPERATION                                      | 29 |

| 5.3 ERROR/STATUS ERROR INDICATION INTERFACE OPERATION                  | 30 |

| 5.4 RESET CONFIGURATION INTERFACE OPERATION                            | 32 |

| 6. SWITCHING CHARACTERISTICS                                           | 33 |

| 6.1 CLOCK AND RESET TIMING PARAMETERS                                  | 33 |

| 6.2 SERIAL SIGNALS TIMING PARAMETERS                                   | 33 |

| 6.3 EXTERNAL PORT TIMING PARAMETERS                                    | 34 |

| 6.4 TIME-CODE INTERFACE TIMING PARAMETERS                              | 35 |

| 6.5 ERROR/STATUS INTERFACE TIMING PARAMETERS                           | 36 |

| 6.6 LATENCY AND JITTER                                                 | -  |

| 6.6.1 Clock Periods                                                    |    |

| <ul><li>6.6.2 Switching Latency</li><li>6.6.3 Router Latency</li></ul> |    |

| 6.6.4 Time-code Latency                                                |    |

| 6.6.5 Time-code Jitter                                                 |    |

| 6.6.6 200M bits/s Input and Output Bit Rate Example                    |    |

| 7. ELECTRICAL CHARACTERISTICS                                          | 40 |

| 7.1 ABSOLUTE MAXIMUM RATINGS                                           | 40 |

| 7.2 DC CHARACTERISTICS                                                 | 40 |

| 7.3 OPERATING TEMPERATURE RANGE                                        | 40 |

| 8. SPACEWIRE ROUTER PACKET TYPES                                       | 41 |

| 8.1 PACKET ADDRESSES                                                   | 41 |

| 8.2 PACKET PRIORITY                                                    | 41 |

| 8.3 PACKET HEADER DELETION                                             | 42 |

| 8.4 INVALID ADDRESSES                                                  | 43 |

| 8.5 DATA PACKETS                                                       | 43 |

| 8.6 COMMAND PACKETS                                                    |    |

| 8.6.1 Supported Commands                                               |    |

| 8.6.2 Read Command                                                     |    |

| Prelimary                                                              | 4  |

Ref.: UoD\_SpW-10X\_

DataSheet

Data-Sheet

| 8.6.3   | Read Incrementing Command               | 49 |

|---------|-----------------------------------------|----|

| 8.6.4   | Read Modify Write Command               |    |

| 8.6.5   | Write Command                           |    |

| 8.6.6   | Command Error Response                  |    |

| 8.6.7   | Command Packet Cyclic Redundancy Check  |    |

| 8.6.8   | Local Source Path Address               |    |

| 8.6.9   | Source Path Address Field               |    |

| 8.6.10  | Command Packet Fill Bytes               |    |

|         |                                         |    |

| 9. CC   | ONTROL LOGIC AND OPERATIONAL MODES      | 68 |

| 9.1 S   | PACEWIRE LINK CONTROL                   | 68 |

| 9.1.1   | Default operating mode                  | 68 |

| 9.1.2   | Auto-Start                              | 68 |

| 9.1.3   | Link-Start                              | 68 |

| 9.1.4   | Link-Disable                            | 69 |

| 9.1.5   | Automatic tri-state enable mode         | 69 |

| 9.1.6   | Setting the data-rate                   | 69 |

| 9.1.7   | Setting the default 10Mbits/s data-rate | 70 |

| 9.1.8   | Data rate comparison table              | 71 |

| 9.2 G   | GLOBAL SPACEWIRE LINK CONTROL           | 71 |

| 9.2.1   | Automatic Link-Start mode               | 71 |

| 9.2.2   | Automatic Link-Disable mode             | 72 |

| 9.3 C   | CONTROL LOGIC AND ROUTING               | 73 |

| 9.3.1   | Packet address error                    |    |

| 9.3.2   | Arbitration                             |    |

| 9.3.2.1 |                                         |    |

| 9.3.2.2 |                                         |    |

| 9.3.2.3 |                                         |    |

| 9.3.2.4 |                                         |    |

| 9.3.3   | Group Adaptive Routing                  |    |

| 9.3.3.1 |                                         |    |

| 9.3.3.2 |                                         |    |

| 9.3.3.3 |                                         |    |

| 9.3.4   | Loop-back routing                       |    |

| 9.3.5   | Packet Blocking                         |    |

| 9.3.5.1 | 5                                       |    |

| 9.3.5.2 | 5                                       |    |

| 9.3.5.3 |                                         |    |

| 9.3.5.4 |                                         |    |

| 9.3.5.5 |                                         |    |

| 9.3.5.6 | -                                       |    |

|         |                                         |    |

Ref.: UoD\_SpW-10X\_

DataSheet

Data-Sheet

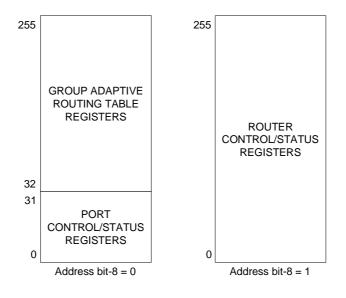

| 10. REGISTER DEFINITIONS                                          | 91  |

|-------------------------------------------------------------------|-----|

| 10.1 INTERNAL MEMORY MAP                                          | 91  |

| 10.2 REGISTER ADDRESSES SUMMARY                                   | 92  |

| 10.3 GROUP ADAPTIVE ROUTING TABLE REGISTERS                       | 93  |

| 10.4 PORT CONTROL/STATUS REGISTERS                                | 95  |

| 10.4.1 Generic port control/status register fields.               | 96  |

| 10.4.2 Configuration port control/status register fields          | 96  |

| 10.4.3 SpaceWire link interface port control/status register bits | 99  |

| 10.4.4 External port control/status register bits                 | 102 |

| 10.5 ROUTER CONTROL/STATUS REGISTERS                              | 102 |

| 10.5.1 Network Discovery Register                                 | 102 |

| 10.5.2 Router Identity Register                                   | 103 |

| 10.5.3 Router Control Register                                    |     |

| 10.5.4 Error active Register                                      |     |

| 10.5.5 Time-Code Register                                         |     |

| 10.5.6 Device Manufacturer and Chip ID Register                   |     |

| 10.5.7 General Purpose Register                                   |     |

| 10.5.8 Time-Code Enable Register                                  |     |

| 10.5.9 Transmit Clock Control Register                            |     |

| 10.5.10 Destination Key Register                                  |     |

| 10.5.11 Unused Registers and Register Bits                        |     |

| 10.5.12 Empty packets                                             |     |

| 10.6 WRITING TO A READ-ONLY REGISTER                              | 113 |

| 11. DOCUMENT CHANGES                                              | 114 |

| 11.1 ISSUE 1.7 TO ISSUE 2.0                                       | 114 |

| 11.2 ISSUE 1.6 TO ISSUE 1.7                                       | 114 |

| 11.3 ISSUE 1.5 TO ISSUE 1.6                                       | 114 |

| 11.4 ISSUE 1.4 TO ISSUE 1.5                                       | 114 |

| 11.5 ISSUE 1.3 TO ISSUE 1.4                                       | 114 |

| 11.6 ISSUE 1.2 TO ISSUE 1.3                                       | 114 |

| 11.7 ISSUE 1.1 TO ISSUE 1.2                                       | 114 |

| 11.8 ISSUE 1.0 TO ISSUE 1.1                                       | 115 |

Ref.:

UoD\_SpW-10X\_

DataSheet

DataSheet

Issue:

2.0

Date:

18<sup>th</sup> August 2006

# I LIST OF FIGURES

| FIGURE 3-1 SPACEWIRE ROUTER BLOCK DIAGRAM                      | . 14 |

|----------------------------------------------------------------|------|

| FIGURE 4-1 CONFIGURATION INTERFACE TIMING SPECIFICATION        | . 26 |

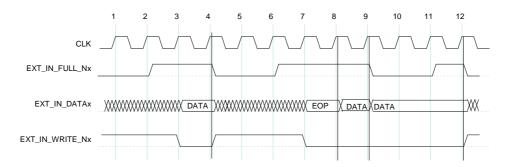

| FIGURE 5-1 EXTERNAL PORT WRITE TIMING SPECIFICATION            | . 28 |

| FIGURE 5-2 EXTERNAL PORT READ TIMING SPECIFICATION             | . 28 |

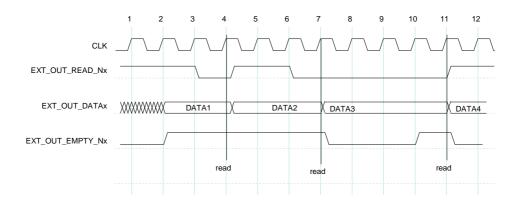

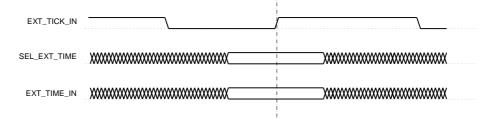

| FIGURE 5-3 TIME-CODE INPUT INTERFACE                           | . 29 |

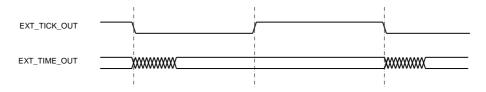

| FIGURE 5-4 TIME-CODE OUTPUT INTERFACE                          | . 29 |

| FIGURE 5-5 TIME-CODE RESET INTERFACE                           | . 30 |

| FIGURE 5-6 STATUS MULTIPLEXER OUTPUT INTERFACE                 | . 30 |

| FIGURE 5-7 RESET CONFIGURATION INTERFACE TIMING SPECIFICATION  | . 32 |

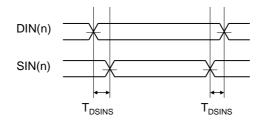

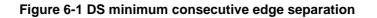

| FIGURE 6-1 DS MINIMUM CONSECUTIVE EDGE SEPARATION              | . 33 |

| FIGURE 6-2 EXTERNAL PORT INPUT FIFO TIMING PARAMETERS          | . 34 |

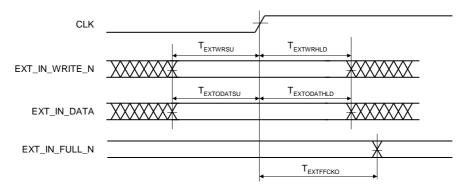

| FIGURE 6-3 EXTERNAL PORT OUTPUT FIFO TIMING PARAMETERS         | . 34 |

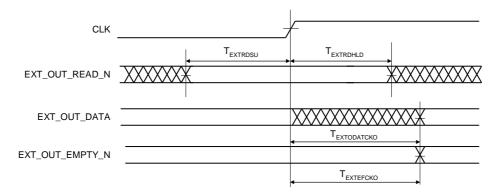

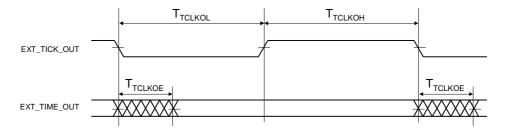

| FIGURE 6-4 TIME-CODE INPUT INTERFACE                           |      |

| FIGURE 6-5 TIME-CODE OUTPUT INTERFACE                          |      |

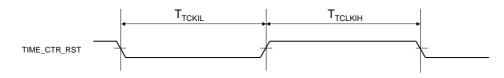

| FIGURE 6-6 TIME_CODE TIME_CTR_RST INTERFACE                    | . 35 |

| FIGURE 8-1 NORMAL ROUTER DATA PACKETS                          |      |

| FIGURE 8-2 COMMAND PACKET FORMAT                               | . 44 |

| FIGURE 8-3 READ SINGLE ADDRESS COMMAND FORMAT                  | . 46 |

| FIGURE 8-4 READ SINGLE ADDRESS REPLY PACKET FORMAT             | . 48 |

| FIGURE 8-5 READ INCREMENTING ADDRESS COMMAND FORMAT            |      |

| FIGURE 8-6 READ INCREMENTING ADDRESS REPLY PACKET FORMAT       |      |

| FIGURE 8-7 READ-MODIFY-WRITE COMMAND PACKET FORMAT             | . 55 |

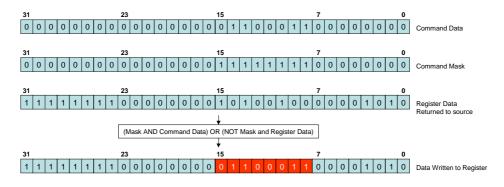

| FIGURE 8-8 READ-MODIFY-WRITE EXAMPLE OPERATION                 | . 57 |

| FIGURE 8-9 READ-MODIFY-WRITE REPLY PACKET FORMAT               | . 58 |

| FIGURE 8-10 WRITE SINGLE ADDRESS COMMAND PACKET.               | . 60 |

| FIGURE 8-11 WRITE SINGLE ADDRESS REPLY PACKET                  | . 62 |

| FIGURE 8-12 SOURCE PATH ADDRESS FIELD DECODING                 | . 67 |

| FIGURE 8-13 SOURCE PATH ADDRESSES IN REPLY PACKET              | . 67 |

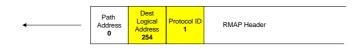

| FIGURE 8-14 NORMAL CONFIGURATION PACKET HEADER STRUCTURE       | . 67 |

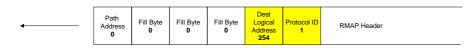

| FIGURE 8-15 FILL BYTES CONFIGURATION HEADER STRUCTURE.         | . 67 |

| FIGURE 9-1 TRI-STATE ENABLE OPERATING MODE.                    | . 69 |

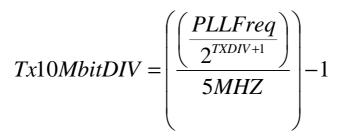

| FIGURE 9-2 TX10MBITDIV EQUATION                                | . 70 |

| FIGURE 9-3 AUTOMATIC LINK-START MODE                           | . 72 |

| FIGURE 9-4 AUTOMATIC LINK-DISABLE MODE                         | . 72 |

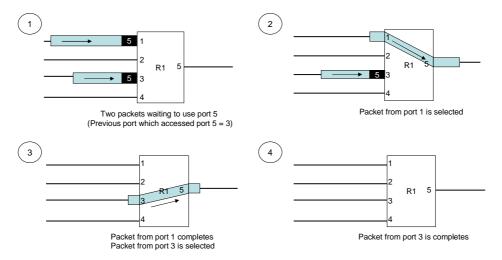

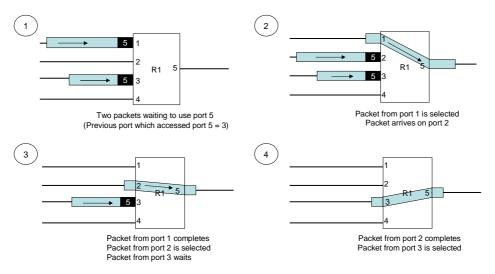

| FIGURE 9-5 ARBITRATION OF TWO PACKETS WITH MATCHING PRIORITY.  | . 74 |

| FIGURE 9-6 ARBITRATION OF THREE PACKETS WITH MATCHING PRIORITY | . 75 |

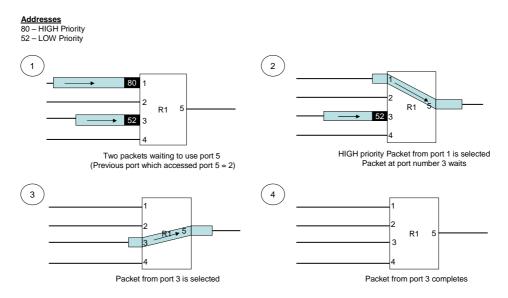

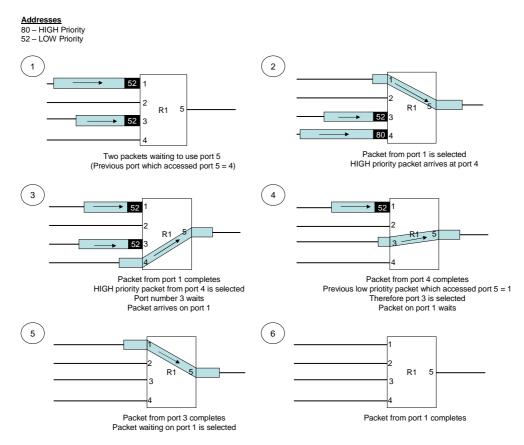

| FIGURE 9-7 ARBITRATION OF TWO PACKETS WITH DIFFERENT PRIORITY  |      |

| FIGURE 9-8                                                     | . 77 |

|                                                                |      |

Ref.: UoD\_SpW-10X\_

DataSheet

18<sup>th</sup> August 2006

Data-Sheet

Issue: 2.0

Date:

FIGURE 10-9 TIME-CODE ENABLE REGISTER FIELDS......110 FIGURE 10-10 TRANSMIT CLOCK CONTROL REGISTER ...... 111

# II LIST OF TABLES

Ref.: UoD\_SpW-10X\_

DataSheet

Data-Sheet

| TABLE 8-1 PACKET ADDRESS MAPPING                             |     |

|--------------------------------------------------------------|-----|

| TABLE 8-2 PACKET PRIORITY MAPPING                            |     |

| TABLE 8-3 PACKET HEADER DELETION MAPPING                     |     |

| TABLE 8-4 SUPPORTED RMAP COMMAND CODES                       |     |

| TABLE 8-5 READ SINGLE ADDRESS CHARACTERISTICS                |     |

| TABLE 8-6 READ SINGLE ADDRESS COMMAND PACKET FIELDS          | 47  |

| TABLE 8-7 READ SINGLE ADDRESS REPLY PACKET FIELDS            |     |

| TABLE 8-8 READ INCREMENTING ADDRESS CHARACTERISTICS          | 50  |

| TABLE 8-9 READ INCREMENTING ADDRESS COMMAND PACKET FIELDS    | 51  |

| TABLE 8-10 READ INCREMENTING ADDRESS REPLY PACKET FIELDS     | 53  |

| TABLE 8-11 READ-MODIFY-WRITE COMMAND CHARACTERISTICS         |     |

| TABLE 8-12 READ-MODIFY-WRITE COMMAND PACKET FIELDS           |     |

| TABLE 8-13 READ-MODIFY-WRITE REPLY PACKET FIELDS             |     |

| TABLE 8-14 WRITE COMMAND CHARACTERISTICS.                    | 59  |

| TABLE 8-15 WRITE SINGLE ADDRESS COMMAND PACKET FIELDS        | 60  |

| TABLE 8-16 WRITE SINGLE ADDRESS REPLY PACKET FIELDS.         |     |

| TABLE 8-17 CONFIGURATION PORT ERRORS SUMMARY                 | 63  |

| Table 8-18 Source Path Address Reference Table               | 66  |

| TABLE 9-1 PORT READY DEFINITIONS                             |     |

| TABLE 9-2 PACKET BLOCKING                                    |     |

| TABLE 10-1 TYPES OF REGISTER WITHIN CONFIGURATION PORT       |     |

| TABLE 10-2 CONFIGURATION REGISTER ADDRESSES                  |     |

| TABLE 10-3 GAR TABLE REGISTER DESCRIPTION                    |     |

| TABLE 10-4 CONFIGURATION PORT CONTROL/STATUS REGISTER FIELDS |     |

| TABLE 10-5 CONFIGURATION PORT CONTROL/STATUS REGISTER FIELDS |     |

| TABLE 10-6 SPACEWIRE PORT CONTROL/STATUS REGISTER FIELDS.    | 100 |

| TABLE 10-7 EXTERNAL PORT CONTOL/STATUS FIELDS                | 102 |

| TABLE 10-8 NETWORK DISCOVERY REGISTER FIELDS                 | 103 |

| TABLE 10-9 ROUTER IDENTITY REGISTER FIELD                    |     |

| TABLE 10-10 ROUTER CONTROL REGISTER FIELDS                   | 105 |

| TABLE 10-11 ERROR ACTIVE REGISTER FIELDS                     | 107 |

| TABLE 10-12 TIME-CODE REGISTER FIELDS                        | 108 |

| TABLE 10-13 DEVICE MANUFACTURER AND CHIP ID REGISTER FIELDS  | 109 |

| TABLE 10-14 TIME-CODE ENABLE REGISTER FIELDS                 | 110 |

| TABLE 10-15 TRANSMIT CLOCK CONTROL REGISTER BITS             |     |

| TABLE 10-16 DESTINATION KEY REGISTER                         |     |

|                                                              |     |

### 1. INTRODUCTION

This document defines a technical reference for the implementation and operation of the SpaceWire Router device, SpW-10X. Detailed timing information for the ASIC implementation is not yet available.

#### 1.1 TERMS AND ACRONYMS

| 3V3  | 3.3 volt interface levels.                                                    |

|------|-------------------------------------------------------------------------------|

| ACK  | Acknowledge                                                                   |

| AD   | Applicable Document                                                           |

| CLK  | Input clock to the SpaceWire router                                           |

| CRC  | Cyclic Redundancy Check                                                       |

| DC   | Direct Current                                                                |

| EEP  | Error end of packet, used to denote an error occurred during packet transfer. |

| EOP  | End of packet used to denote a normal end of packet in SpaceWire.             |

| FIFO | First in - First out buffer used to transfer data between logic.              |

| FPGA | Field Programmable Gate Array.                                                |

| LVDS | Low voltage differential signalling.                                          |

| NACK | Negative acknowledge (error acknowledge)                                      |

| RD   | Read                                                                          |

| RMAP | Remote Memory Access Protocol                                                 |

| RST  | Aysnchronous reset to the SpaceWire router.                                   |

| UoD  | University of Dundee.                                                         |

| WR   | Write                                                                         |

#### 1.2 DOCUMENTS

In this section the documents referenced in this document are listed.

Ref.: UoD\_SpW-10X\_ DataSheet Issue: 2.0

Data-Sheet

Date: 18<sup>th</sup> August 2006

| Table 1-1 Applicable Documents |                     |                                                 |  |

|--------------------------------|---------------------|-------------------------------------------------|--|

| REF                            | Document Number     | Document Title                                  |  |

| AD1                            | ECSS-E5O-12A        | SpaceWire - links, nodes, routers and networks. |  |

| AD2                            | ECSS-E50-11 Draft E | SpaceWire Remote Memory Access Protocol         |  |

### 2. APPLICATIONS

The SpaceWire router applications are defined in the following sections

### 2.1 STAND-ALONE ROUTER

The SpaceWire Router may be used as a stand-alone router with up to eight SpaceWire links connected to it. Configuration of the routing tables etc. may be done by sending SpaceWire packets containing configuration commands to the router.

#### 2.2 NODE INTERFACE

The SpaceWire Router has two external ports which enable the device to be used as a node interface. The equipment to be connected to the SpaceWire network is attached to one or both external ports. One or more SpaceWire ports are used to provide the connection into the SpaceWire network. Unused SpaceWire ports may be disabled and their outputs tri-stated to save power. In this arrangement configuration of the routing tables and other parameters may be done by sending configuration packets from the local host via an external port or from a remote network manager via a SpaceWire port.

#### 2.3 EMBEDDED ROUTER

The SpaceWire Router device can also be used to provide a node with an embedded router. In this case the external ports are used to provide the local connections to the node and the SpaceWire ports are used to make connections to other ports in the network. The difference between this configuration and that of section 2.2 is just a conceptual one with the Node interface configuration normally using fewer SpaceWire ports than the Embedded Router configuration.

### 2.4 EXPANDING THE NUMBER OF ROUTER PORTS

If a routing switch with a larger number of SpaceWire (or external) ports is required then this can be accomplished by joining together two or more routers using some of the SpaceWire links. For example using two SpaceWire links to join together two router devices would create an effective router with twelve SpaceWire ports and four external ports. Note, however, that an extra path addressing byte is needed to route packets between the two routers and that there is additional routing delay.

#### 3. FUNCTIONAL OVERVIEW

A SpaceWire routing switch is able to connect together many nodes, providing a means of routing packets between the nodes connected to it. It comprises a number of SpaceWire link interfaces and a routing matrix. The routing matrix enables packets arriving at one link interface to be transferred to and sent out of another link interface on the routing switch

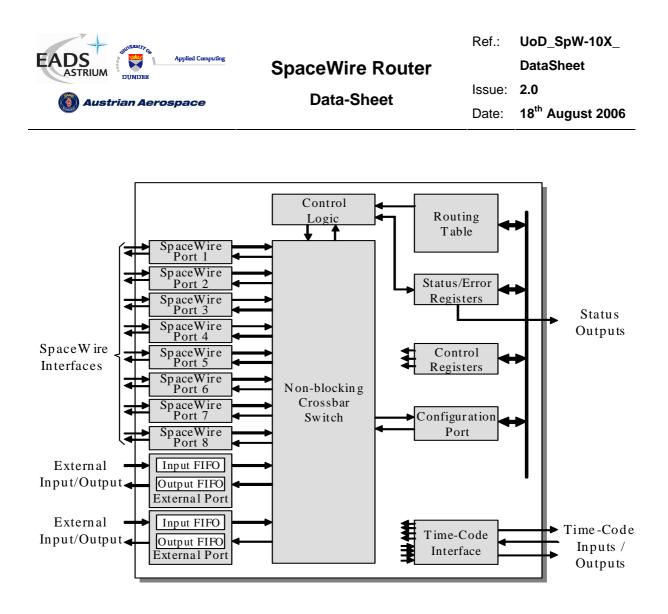

The SpaceWire router comprises the following functional logic blocks:

- Eight SpaceWire bi-directional serial ports.

- Two external parallel input/output ports each comprising an input FIFO and an output FIFO.

- A non-blocking crossbar switch connecting any input port to any output port.

- An internal configuration port accessible via the crossbar switch from the external parallel input/output port or the SpaceWire input/output ports.

- A routing table accessible via the configuration port which holds the logical address to output port mapping.

- Control logic to control the operation of the switch, performing arbitration and group adaptive routing.

- Control registers than can be written and read by the configuration port and which hold control information e.g. link operating speed.

- An external time-code interface comprising tick\_in, tick\_out and current tick count value

- Internal status/error registers accessible via the configuration port

- External status/error signals

A block diagram of the routing switch is given in Figure 3-1.

Figure 3-1 SpaceWire router block diagram

The following paragraphs define the SpaceWire router functional logic blocks in more detail.

### 3.1 SPACEWIRE PORTS

The SpaceWire router has eight bi-directional SpaceWire links each conformant with the SpaceWire standard. Each SpaceWire link is controlled by an associated link register and routing control logic. Network level error recovery is performed when an error is detected on the SpaceWire link as defined in the SpaceWire standard. Packets received on SpaceWire links are routed by the routing control logic to the configuration port, other SpaceWire link ports or the external FIFO ports. Packets with invalid addresses are discarded by the SpaceWire router dependent on the packet address. The SpaceWire link status is recorded in the associated link register and error status is held by the router until cleared by a configuration command.

### 3.2 EXTERNAL PORTS

The SpaceWire router has two bi-directional parallel FIFO interfaces to an external host system. Each FIFO is written to or read from synchronously to the 30MHz system clock. An eight-bit data interface and an extra control bit for end of packet markers are provided by each external port FIFO. Packets

| HUNDRENT CA           |                  | Ref.:  | UoD_SpW-10X_                 |

|-----------------------|------------------|--------|------------------------------|

| EADS<br>ASTRIUM       | SpaceWire Router |        | DataSheet                    |

| () Austrian Aerospace | Data-Sheet       | Issue: | 2.0                          |

|                       |                  | Date:  | 18 <sup>th</sup> August 2006 |

received by the external port are routed by the routing control logic to the configuration port, SpaceWire link ports or the other external port dependent on the packet address. Packets with invalid addresses are discarded by the SpaceWire router.

# 3.3 CONFIGURATION PORT

The SpaceWire router has one configuration port which performs read and write operations to internal router registers. Packets are routed to the configuration port when a packet with a leading address byte of zero is received. The command packet format used in the SpaceWire Router is the Remote Memory Access Protocol (RMAP) [AD2]. A detailed description of the format of the RMAP command packets is defined in section 8.6. If an invalid command packet is received then the error is flagged to the associated status register and the packet is discarded. The internal router registers are described in section 0.

### 3.4 ROUTING TABLE

The SpaceWire router routing table is set by the router command packets to assign logical addresses to physical destination ports on the router. A group of destination ports can be set, in each routing table location, to enable group adaptive routing. In group adaptive routing a packet can be routed to its destination through one of a set of output ports dependent on which ports in the set are free to use. When a packet is received with a logical address the routing table is checked by the routing control logic and the packet is routed to the destination port when the port is ready.

Routing table locations are set to invalid at power on or at reset. An invalid routing address will cause the packet to be spilled by the control logic. The routing table logical addresses can also be set to support high priority and header deletion. High priority packets are routed before low priority packets and header deletion of logical addresses can be used to support regional logical addressing (see AD1).

### 3.5 ROUTING CONTROL LOGIC AND CROSSBAR

The routing control logic is responsible for arbitration of output ports, group adaptive routing and the crossbar switching. Arbitration is performed when two or more source ports are requesting to use the same destination port. A priority based arbitration scheme with two priority levels, high and low, is used where high priority packets are routed before low priority packets. Fair arbitration is performed on packets which have the same priority levels to ensure each packet gets equal access to the output port.

Group adaptive routing control selects one of a number of output ports for sending out the source packet.

### 3.6 TIME-CODE PROCESSING

An internal time-code register is used in the router to allow the router to be a time-code master or a time-code slave.

In master mode the time-code interface is used to provide a tick-in to the SpaceWire routing causing time-codes to be propagated through the network. Two modes of time master operation are supported, an automatic mode where a time-code is propagated on each external tick-in and a normal mode where the time-code is propagated dependent on the external time-in signal.

In time-code slave mode a valid received time-code, one plus the value of the router time-code register, causes a tick-out to be sent to the SpaceWire links and the external time-code interface. The time-code is propagated to all time-code ports except the port on which the time-code was received. If the time-code received is not one plus the value of the time-code register then the time-code register is updated but the tick-out is not performed. In this way circular network paths do not cause a constant stream of time-codes to be sent in a loop.

### 3.7 CONTROL/STATUS REGISTERS

The control and status registers in the SpaceWire router provide the means to control the operation of the router, set the router configuration and parameters or monitor the status of the device. The registers are accessed using RMAP [AD2] commands packets received by the configuration port.

#### 4. DEVICE INTERFACE

The device pins used by each interface are described in this section. There is a table for each type of interface listing the signals in that interface. These tables have the following fields:

- Pin No: The device pin number

- Signal: The name of the signal

- Dir: The direction of the signal; in, out or in/out

- Description: An explanation of what the signal does.

- Type: The type of signal

The sections below define the pin out of the SpaceWire router. Its interfaces are split into several types, separated by headings for clarity:

- Global signals: clock and reset

- SpaceWire interface signals

- External port signals

- Time-code interface signals

- Configuration signals

- Reset configuration signals

- Power and Ground

The following signal types are used in the SpaceWire Router:

- CMOS3V3 3.3 Volt CMOS logic

- LVDS Low Voltage Differential Signal

- 3V3 3.3 Volt power

- GND 0 Volt ground

#### 4.1 GLOBAL SIGNALS

The global system clock and reset signals are listed in Table 4-1.

|       | Table 4-1 Global Signals      |    |                                                                                            |         |  |  |  |  |  |

|-------|-------------------------------|----|--------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| PinNo | PinNoSignalDirDescriptionType |    |                                                                                            |         |  |  |  |  |  |

|       | CLK                           | In | System clock. Provides the reference clock for all modules except the interface receivers. | CMOS3V3 |  |  |  |  |  |

|       | RST_N                         | In | Asynchronous system reset (active low)                                                     | CMOS3V3 |  |  |  |  |  |

| EEADS<br>ASTRIUM |                   |     | SpaceWire Router                                                                                                                      | Ref.:<br>Issue: | UoD_SpW-10X_<br>DataSheet<br>2.0 |            |

|------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|------------|

|                  | 🥘 Austrian Aerosp | ace | Data-Sheet                                                                                                                            | Date:           | 18 <sup>th</sup> Au              | igust 2006 |

|                  | FEEDBDIV(2:0)     | In  | Set the output clock rate of the internal F<br>"000" $\rightarrow$ 100MHz<br>"001" $\rightarrow$ 120MHz<br>"010" $\rightarrow$ 140MHz | PLL as fo       | llows:                           | CMOS3V3    |

"011" → 160MHz

"100" → 180MHz

"101" → 200MHz

"110" → 200MHz

"111" → 200MHz

#### 4.2 SPACEWIRE SIGNALS

The SpaceWire interface signals are listed in Table 4-2. For further details about SpaceWire see the SpaceWire standard [AD1].

See section 9.1.6 for setting the transmit rate.

|       | Table 4-2 Data and Strobe SpaceWire Signals |     |                                                    |                 |  |  |  |  |  |

|-------|---------------------------------------------|-----|----------------------------------------------------|-----------------|--|--|--|--|--|

| PinNo | Signal                                      | Dir | Description                                        | Туре            |  |  |  |  |  |

|       | DOUT+(1)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(1)                                    |     | SpaceWire link 1.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(2)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(2)                                    |     | SpaceWire link 2.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(3)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(3)                                    |     | SpaceWire link 3.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(4)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(4)                                    |     | SpaceWire link 4.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(5)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(5)                                    |     | SpaceWire link 5.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(6)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(6)                                    |     | SpaceWire link 6.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(7)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(7)                                    |     | SpaceWire link 7.                                  | LVDS - (N Side) |  |  |  |  |  |

|       | DOUT+(8)                                    | Out | Differential output pair, data part of Data-Strobe | LVDS+ (P Side)  |  |  |  |  |  |

|       | DOUT-(8)                                    |     | SpaceWire link 8.                                  | LVDS - (N Side) |  |  |  |  |  |

Ref.: UoD\_SpW-10X\_

DataSheet

### Data-Sheet

Issue: 2.0

Date: 18<sup>th</sup> August 2006

| SOUT+(1) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

|----------|----------|------------------------------------------------------|-----------------|

| SOUT-(1) |          | SpaceWire link 1.                                    | LVDS - (N Side) |

|          |          |                                                      | ``````          |

| SOUT+(2) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(2) |          | SpaceWire link 2.                                    | LVDS - (N Side) |

| SOUT+(3) | Out      |                                                      | LVDS+ (P Side)  |

| SOUT-(3) |          | SpaceWire link 3.                                    | LVDS - (N Side) |

| SOUT+(4) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(4) |          | SpaceWire link 4.                                    | LVDS - (N Side) |

| SOUT+(5) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(5) |          | SpaceWire link 5.                                    | LVDS - (N Side) |

| SOUT+(6) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(6) |          | SpaceWire link 6.                                    | LVDS - (N Side) |

| SOUT+(7) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(7) |          | SpaceWire link 7.                                    | LVDS - (N Side) |

| SOUT+(8) | Out      | Differential output pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SOUT-(8) |          | SpaceWire link 8.                                    | LVDS - (N Side) |

| DIN+(1)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(1)  |          | SpaceWire link 1.                                    | LVDS - (N Side) |

| DIN+(2)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(2)  |          | SpaceWire link 2.                                    | LVDS - (N Side) |

| DIN+(3)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(3)  |          | SpaceWire link 3.                                    | LVDS - (N Side) |

| DIN+(4)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(4)  |          | SpaceWire link 4.                                    | LVDS - (N Side) |

| DIN+(5)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(5)  |          | SpaceWire link 5.                                    | LVDS - (N Side) |

| DIN+(6)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(6)  |          | SpaceWire link 6.                                    | LVDS - (N Side) |

| DIN+(7)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(7)  | <u> </u> | SpaceWire link 7.                                    | LVDS - (N Side) |

| DIN+(8)  | In       | Differential input pair, data part of Data-Strobe    | LVDS+ (P Side)  |

| DIN-(8)  |          | SpaceWire link 8.                                    | LVDS - (N Side) |

| SIN+(1)  | In       | Differential input pair, strobe part of Data-Strobe  | LVDS+ (P Side)  |

| SIN-(1)  | <u> </u> | SpaceWire link 1.                                    | LVDS - (N Side) |

| SIN+(2)  | In       | Differential input pair, strobe part of Data-Strobe  | LVDS+ (P Side)  |

| SIN-(2)  |          | SpaceWire link 2.                                    | LVDS - (N Side) |

| SIN+(3)  | In       | Differential input pair, strobe part of Data-Strobe  | LVDS+ (P Side)  |

| SIN-(3)  | <u> </u> | SpaceWire link 3.                                    | LVDS - (N Side) |

| SIN+(4)  | In       | Differential input pair, strobe part of Data-Strobe  | LVDS+ (P Side)  |

Ref.: UoD\_SpW-10X\_ DataSheet Issue: 2.0

Data-Sheet

Date: 18<sup>th</sup> August 2006

| SIN-(4) |    | SpaceWire link 4.                                   | LVDS - (N Side) |

|---------|----|-----------------------------------------------------|-----------------|

| SIN+(5) | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SIN-(5) |    | SpaceWire link 5.                                   | LVDS - (N Side) |

| SIN+(6) | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SIN-(6) |    | SpaceWire link 6.                                   | LVDS - (N Side) |

| SIN+(7) | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SIN-(7) |    | SpaceWire link 7.                                   | LVDS - (N Side) |

| SIN+(8) | In | Differential input pair, strobe part of Data-Strobe | LVDS+ (P Side)  |

| SIN-(8) |    | SpaceWire link 8.                                   | LVDS - (N Side) |

# 4.3 EXTERNAL PORT DATA SIGNALS

The External port signals are listed in Table 4-3. The timing of these signals is shown in Figure 5-1 External port write timing specification and Figure 5-2 External port read timing specification.

|       | Table 4-3 External Port Interface Signals                                                                                                                                        |     |                                                                                                                                                                                                                                                                                           |         |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| PinNo | Signal                                                                                                                                                                           | Dir | Description                                                                                                                                                                                                                                                                               | Туре    |  |  |  |

|       | EXT_OUT_DATA0(8)<br>EXT_OUT_DATA0(7)<br>EXT_OUT_DATA0(6)<br>EXT_OUT_DATA0(5)<br>EXT_OUT_DATA0(4)<br>EXT_OUT_DATA0(3)<br>EXT_OUT_DATA0(2)<br>EXT_OUT_DATA0(1)<br>EXT_OUT_DATA0(0) | Out | Output data from external port zero FIFO. Bit<br>eight determines the type - data, EOP or EEP.<br>The encodings are defined as:<br>(8)(70) – <b>Bits</b><br>(0)(ddddddd) - Data byte<br>(1)(XXXXXX0) - EOP.<br>(1)(XXXXXX1) - EEP.<br>Bit 7 is the most significant bit of the data byte. | CMOS3V3 |  |  |  |

|       | EXT_OUT_EMPTY_N0                                                                                                                                                                 | Out | FIFO ready signal for external output port zero.<br>When high the FIFO has data. When low the<br>FIFO is empty.                                                                                                                                                                           | CMOS3V3 |  |  |  |

|       | EXT_OUT_READ_N0                                                                                                                                                                  | In  | Asserted (low) to read from the external output port zero FIFO.                                                                                                                                                                                                                           | CMOS3V3 |  |  |  |

|       | EXT_IN_DATA0(8)<br>EXT_IN_DATA0(7)<br>EXT_IN_DATA0(6)                                                                                                                            | In  | Input data to external port zero FIFO. Bit eight determines the type - data, eop or eep. The encodings are defined as:                                                                                                                                                                    | CMOS3V3 |  |  |  |

Ref.: UoD\_SpW-10X\_

DataSheet

Issue: 2.0

Date: 18<sup>th</sup> August 2006

| <br>EVT IN DATAO(5)  |     |                                                                                             |           |

|----------------------|-----|---------------------------------------------------------------------------------------------|-----------|

| EXT_IN_DATA0(5)      |     | (8)(70) - Bits                                                                              |           |

| EXT_IN_DATA0(4)      |     | (0)(ddddddd) - Data byte<br>(1)(xxxxxx0) - EOP.                                             |           |

| EXT_IN_DATA0(3)      |     | (1)(XXXXXX1) - EEP.                                                                         |           |

| EXT_IN_DATA0(2)      |     |                                                                                             |           |

| EXT_IN_DATA0(1)      |     | Bit 7 is the most significant bit of the data byte.                                         |           |

| EXT_IN_DATA0(0)      |     |                                                                                             |           |

| <br>EXT_IN_FULL_N0   | Out | FIFO ready signal for external input port zero.                                             | CMOS3V3   |

|                      |     | When high there is space in the FIFO so it can                                              |           |

|                      |     | be written to. When low the FIFO is full.                                                   |           |

| EXT_IN_WRITE_N0      | In  | Asserted (low) to write to the external input port                                          | CMOS3V3   |

| <br>EXT OUT DATA1(8) | 0   | zero FIFO.                                                                                  | CMOS3V3   |

| `,                   | Out | Output data from external port one FIFO . Bit eight determines the type - data, eop or eep. | CIVIO53V3 |

| EXT_OUT_DATA1(7)     |     | The encodings are defined as:                                                               |           |

| EXT_OUT_DATA1(6)     |     |                                                                                             |           |

| EXT_OUT_DATA1(5)     |     | (8)(70) – <b>Bits</b>                                                                       |           |

| EXT_OUT_DATA1(4)     |     | (0)(ddddddd) - Data byte                                                                    |           |

| EXT_OUT_DATA1(3)     |     | (1)(XXXXXX0) - EOP.                                                                         |           |

| EXT_OUT_DATA1(2)     |     | (1)(XXXXXX1) - EEP.                                                                         |           |

| EXT_OUT_DATA1(1)     |     | Bit 7 is the most significant bit of the data byte.                                         |           |

|                      |     |                                                                                             |           |

| EXT_OUT_DATA1(0)     |     |                                                                                             |           |

| EXT_OUT_EMPTY_N1     | Out | FIFO ready signal for external output port one.                                             | CMOS3V3   |

|                      |     | When high the FIFO has data. When low the                                                   |           |

| EXT OUT READ N1      | In  | FIFO is empty.                                                                              |           |

| EXT_OUT_READ_NT      | 111 | Asserted (low) to read from the external output port one FIFO.                              | CMOS3V3   |

| EXT_IN_DATA1(8)      | In  | Input data to external port one FIFO. Bit eight                                             | CMOS3V3   |

| EXT_IN_DATA1(7)      |     | determines the type - data, eop or eep. The                                                 |           |

| EXT_IN_DATA1(6)      |     | encodings are defined as:                                                                   |           |

| EXT_IN_DATA1(5)      |     | (8)(70) <b>– Bits</b>                                                                       |           |

|                      |     | (0)(ddddddd) - Data byte                                                                    |           |

| EXT_IN_DATA1(4)      |     | (1)(XXXXXX0) - EOP.                                                                         |           |

| EXT_IN_DATA1(3)      |     | (1)(XXXXXX1) - EEP.                                                                         |           |

| EXT_IN_DATA1(2)      |     |                                                                                             |           |

| EXT_IN_DATA1(1)      |     | Bit 7 is the most significant bit of the data byte.                                         |           |

| I                    |     |                                                                                             |           |

Issue: 2.0

Date: 18<sup>th</sup> August 2006

| EXT_IN_DATA1(0) |     |                                                    |         |

|-----------------|-----|----------------------------------------------------|---------|

| EXT_IN_FULL_N1  | Out | FIFO ready signal for external input port one.     | CMOS3V3 |

|                 |     | When high there is space in the FIFO so it can     |         |

|                 |     | be written to. When low the FIFO is full.          |         |

| EXT_IN_WRITE_N1 | In  | Asserted (low) to write to the external input port | CMOS3V3 |

|                 |     | one FIFO.                                          |         |

# 4.4 TIME-CODE SIGNALS

The time-code interface signals are listed in Table 4-4. The timing of this interface is shown in Figure 5-3 and Figure 5-4.

|       | Table 4-4 Time-Code Signals |     |                                                          |         |  |  |  |

|-------|-----------------------------|-----|----------------------------------------------------------|---------|--|--|--|

| PinNo | Signal                      | Dir | Description                                              | Туре    |  |  |  |

|       | EXT_TICK_IN                 | In  | The rising edge of the EXT_TICK_IN signal is used        | CMOS3V3 |  |  |  |

|       |                             |     | to indicate when a time-code is to be sent. On the       |         |  |  |  |

|       |                             |     | rising edge of the EXT_TICK_IN signal the                |         |  |  |  |

|       |                             |     | SEL_EXT_TIME signal is sampled to determine if           |         |  |  |  |

|       |                             |     | the time-code value is to be provided by the internal    |         |  |  |  |

|       |                             |     | time-counter or by the external time input               |         |  |  |  |

|       |                             |     | EXT_TIME_IN(7:0).                                        |         |  |  |  |

|       |                             |     | The SEL_EXT_TIME and the EXT_TIME_IN(7:0)                |         |  |  |  |

|       |                             |     | signals must be set up prior to the rising edge of       |         |  |  |  |

|       |                             |     | EXT_TICK_IN and must be held static sometime             |         |  |  |  |

|       |                             |     | afterwards.                                              |         |  |  |  |

|       | EXT_TIME_IN(7)              | In  | EXT_TIME_IN(7:0) provides the value of the time-         | CMOS3V3 |  |  |  |

|       | EXT_TIME_IN(6)              |     | code to be distributed by the router when an             |         |  |  |  |

|       | EXT_TIME_IN(5)              |     | external time-code source is selected i.e. when          |         |  |  |  |

|       | EXT_TIME_IN(4)              |     | SEL_EXT_TIME is high on the rising edge of               |         |  |  |  |

|       | EXT_TIME_IN(3)              |     | EXT_TICK_IN.                                             |         |  |  |  |

|       | EXT_TIME_IN(2)              |     |                                                          |         |  |  |  |

|       | EXT_TIME_IN(1)              |     | When <b>SEL_EXT_TIME</b> is high on the rising edge of   |         |  |  |  |

|       | EXT_TIME_IN(0)              |     | <b>EXT_TICK_IN</b> the value of the time-code counter is |         |  |  |  |

|       |                             |     | used for bits 5:0 of the time-code and bits 7:6 of the   |         |  |  |  |

|       |                             |     | EXT_TIME_IN(7:0) are used for the two control            |         |  |  |  |

|       |                             |     | signals, bits 7:6 of the time-code.                      |         |  |  |  |

|       | SEL_EXT_TIME                | In  | If SEL_EXT_TIME is high on the rising edge of            | CMOS3V3 |  |  |  |

|       |                             |     | EXT_TICK_IN the value on EXT_TIME_IN(7:0) is             |         |  |  |  |

|       |                             |     | loaded into the internal time-code register and          |         |  |  |  |

Ref.: UoD\_SpW-10X\_ DataSheet

Data-Sheet

Issue: 2.0

Date: 18<sup>th</sup> August 2006

|   |                 |     | propagated by the router.                              |         |

|---|-----------------|-----|--------------------------------------------------------|---------|

|   |                 |     |                                                        |         |

|   |                 |     | If <b>SEL_EXT_TIME</b> is low on the rising edge of    |         |

|   |                 |     | EXT_TICK_IN the value to be sent in the time-code      |         |

|   |                 |     | will be taken from the internal time-code counter in   |         |

|   |                 |     | the router. The two control-bits (bits 7:6) of the     |         |

|   |                 |     | time-code will come from bits 7:6 of the               |         |

|   |                 |     | EXT_TIME_IN(7:0)input.                                 |         |

|   | TIME_CTR_RST    | In  | This signal causes the internal time-code counter to   | CMOS3V3 |

|   |                 |     | be reset to zero.                                      |         |

|   |                 |     |                                                        |         |

|   |                 |     | The timing parameters used for <b>EXT_TICK_IN</b> also |         |

|   |                 |     | apply to the time-code counter reset signal            |         |

|   |                 |     | (TIME_CTR_RST).                                        |         |

|   | EXT_TICK_OUT    | Out |                                                        | CMOS3V3 |

|   |                 |     | indicated the reception of a time-code. The value of   |         |

|   |                 |     | this time-code is place on the                         |         |

|   |                 |     | EXT_TIME_OUT(7:0)outputs and is valid on the           |         |

|   |                 |     | rising edge of EXT_TICK_OUT.                           |         |

|   | EXT_TIME_OUT(7) | Out |                                                        | CMOS3V3 |

|   | EXT_TIME_OUT(6) |     | EXT_TICK_OUT is asserted.                              |         |

|   | EXT_TIME_OUT(5) |     |                                                        |         |

|   | EXT_TIME_OUT(4) |     | The value of a received time-code is output on the     |         |

|   | EXT_TIME_OUT(3) |     | falling edge of <b>EXT_TICK_OUT</b> . The              |         |

|   | EXT_TIME_OUT(2) |     | <b>EXT_TIME_OUT(7:0)</b> value is held until the next  |         |

|   | EXT_TIME_OUT(1) |     | time-code is output.                                   |         |

|   | EXT_TIME_OUT(0) |     |                                                        |         |

|   |                 |     |                                                        |         |

| L | I               | 1   |                                                        |         |

### 4.5 LINK ERROR INDICATION SIGNALS

The link error indication signals are listed in Table 4-5.

|       | Table 4-5 Link error indication Signals                  |     |                                                                                                         |                |  |  |

|-------|----------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------|----------------|--|--|

| PinNo | Signal                                                   | Dir | Description                                                                                             | Signal<br>Type |  |  |

|       | STAT_MUX_ADDR(3)<br>STAT_MUX_ADDR(2)<br>STAT_MUX_ADDR(1) | in  | Select the error indication status signals to be output on <b>STAT_MUX_OUT</b> as defined in Table 5-1. | CMOS3V3        |  |  |

Ref.: UoD\_SpW-10X\_

DataSheet

Data-Sheet

Issue: 2.0

Date: 18<sup>th</sup> August 2006

| STAT_MUX_ADDR(0) |       |                                                 |         |

|------------------|-------|-------------------------------------------------|---------|

| STAT_MUX_OUT(7)  | inout | Multi function pin.                             | CMOS3V3 |

| STAT_MUX_OUT(6)  |       | Power on Configuration                          |         |

| STAT_MUX_OUT(5)  |       | After reset the <b>STAT_MUX_OUT</b> pins are    |         |

| STAT_MUX_OUT(4)  |       | inputs which define the power on configuration  |         |

| STAT_MUX_OUT(3)  |       | status of the router. The pin mappings are      |         |

| STAT_MUX_OUT(2)  |       | listed in section 5.1.6.                        |         |

| ,                |       | Normal Operation                                |         |

| STAT_MUX_OUT(1)  |       | After the power on reset configuration of the   |         |

| STAT_MUX_OUT(0)  |       | router has been read from STAT_MUX_OUT          |         |

|                  |       | the pins are driven as outputs by the router.   |         |

|                  |       | The function of these output pins is defined by |         |

|                  |       | STAT_MUX_ADDR(3:0).                             |         |

|                  |       |                                                 |         |

# 4.6 RESET CONFIGURATION SIGNALS

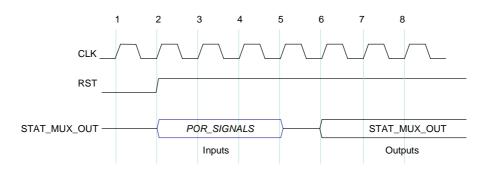

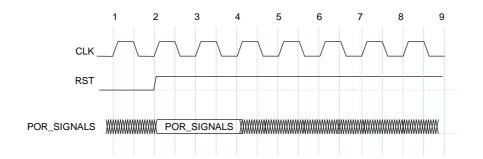

The Reset Configuration signals are listed in Table 4-6. These signals are input on **STAT\_MUX\_OUT** after reset to initialise the router. They are not used at any other time except immediately after reset. The Reset Configuration signals set relevant bits in the configuration registers (see section 0). Following reset the values of these signals are synchronously loaded into the router. The timing of the Reset Configuration signals is illustrated in Figure 5-7.

Data-Sheet

Ref.: UoD\_SpW-10X\_

DataSheet

| Table 4-6 Reset Configuration Signals |                       |                                                  |                |  |

|---------------------------------------|-----------------------|--------------------------------------------------|----------------|--|

| Signal                                | Dir                   | Description                                      | Signal<br>Type |  |

| STAT_MUX_OUT(2:0)                     | In                    | Sets the transmitter maximum data rate after     | CMOS3V3        |  |

| [maps to -> POR_TX_RATE(2:0)]         |                       | reset. The data rate can subsequently be         |                |  |

|                                       |                       | changed during normal operation using port       |                |  |

|                                       |                       | configuration commands. The values are           |                |  |

|                                       |                       | listed below.                                    |                |  |

|                                       |                       | "111" – Full data rate after link start-up.      |                |  |

|                                       |                       | "110" – 1/2 data rate after link start-up.       |                |  |

|                                       |                       | "101" – 1/3 data rate after link start-up.       |                |  |

|                                       |                       | "100" – 1/4 data rate after link start-up.       |                |  |

|                                       |                       | "011" – 1/5 data rate after link start-up.       |                |  |

|                                       |                       | "010" – 1/6 data rate after link start-up.       |                |  |

|                                       |                       | "001" – 1/7 data rate after link start-up.       |                |  |

|                                       |                       | "000" – 1/8 data rate after link start-up.       |                |  |

|                                       |                       | Note: <b>POR_TX_RATE</b> affects all SpaceWire   |                |  |

|                                       |                       | ports in the router.                             |                |  |

|                                       |                       | Note: The data rate is dependent on              |                |  |

|                                       |                       | FEEDBDIV at reset                                |                |  |

| STAT_MUX_OUT(3)                       | In                    | If asserted (low) after reset allows a router    | CMOS3V3        |  |

| [maps to ->                           |                       | port to address itself and therefore cause an    |                |  |

| POR_ADDR_SELF_N                       |                       | input packet to be returned through the same     |                |  |

|                                       | input port. This mode |                                                  |                |  |

|                                       |                       | debug and test operations.                       |                |  |

|                                       |                       | This signal is active low.                       |                |  |

| STAT_MUX_OUT(4)                       | In                    | Power on reset signal which determines if        | CMOS3V3        |  |

| [maps to ->                           |                       | output port timeouts are enabled at start-up.    |                |  |

| POR_TIMEOUT_EN_N]                     |                       | When asserted (low) the port timeouts are        |                |  |

|                                       |                       | enabled. When de-asserted (high) they are        |                |  |

|                                       |                       | disabled.                                        |                |  |

|                                       |                       | This signal is active low.                       |                |  |

| STAT_MUX_OUT(5)                       | In                    | Power on reset value which determines the        | CMOS3V3        |  |

| [maps to ->                           |                       | initial timeout value. The following values      |                |  |

| POR_SEL_TIMEOUT0_N]                   |                       | determine which timeout is selected at power up. |                |  |

|                                       |                       |                                                  |                |  |

|                                       |                       | '1' => Timeout period is ~ 100 us.               |                |  |

|                                       |                       | '0' => Timeout period is ~ 1.3 s.                |                |  |

Ref.: UoD\_SpW-10X\_ DataSheet

DataSi

🔞 Austrian Aerospace

Data-Sheet

Issue: 2.0

Date: 18<sup>th</sup> August 2006

|                         |    | Timeout Period is:<br>'1' => 200x(2^2)x(10 MHz clk period) |         |

|-------------------------|----|------------------------------------------------------------|---------|

|                         |    | '0' => 200x(2^16)x(10 MHz clk period)                      |         |

| STAT_MUX_OUT(6)         | In | Power on reset signal which determines if the              | CMOS3V3 |

| [maps to ->             |    | output ports automatically start up when they              |         |

| POR_START_ON_REQ_N]     |    | are the destination address of a packet.                   |         |

|                         |    | When asserted (low) the output port will                   |         |

|                         |    | automatically start on request.                            |         |

|                         |    | This signal is active low.                                 |         |

| STAT_MUX_OUT(7)         | In | Power on reset signal which determines if the              | CMOS3V3 |

| [maps to ->             |    | output ports are disabled when no activity is              |         |

| POR_DSBLE_ON_SILENCE_N] |    | detected on an output port for the current                 |         |

|                         |    | timeout period.                                            |         |

|                         |    | When asserted (low) an output port is                      |         |

|                         |    | disabled when it has not sent any information              |         |

|                         |    | for longer than the current timeout period.                |         |

|                         |    | This signal is active low.                                 |         |

Figure 4-1 Configuration interface timing specification

The POR configuration signals (POR\_SIGNALS) listed in Table 4-6 are loaded into the appropriate internal configuration registers of the router after **RST** is de-asserted. To make sure that the POR configuration signal values are loaded properly they should be held stable for at least three **CLK** cycles following **RST** being de-asserted. The status output **STAT\_MUX\_OUT** is driven on the fourth **CLK** cycle after **RST** is de-asserted.

Note: The recommended method for setting the POR signals is to use external pull up/down resistors in which case the timing of the POR signals is not critical.

Ref.:

UoD\_SpW-10X\_

18<sup>th</sup> August 2006 Date:

# 4.7 POWER AND GROUND SIGNALS

The Power and Ground connections are listed in Table 4-6.

|        | Table 4-7 Reset Configuration Signals |                                  |                |  |  |

|--------|---------------------------------------|----------------------------------|----------------|--|--|

| Signal | Dir                                   | Description                      | Signal<br>Type |  |  |

| Power  | -                                     | 3.3 V power for the device       | 3V3            |  |  |

| Ground | -                                     | Ground connection for the device | GND            |  |  |

#### 5. INTERFACE OPERATIONS

#### 5.1 EXTERNAL PORT INTERFACE OPERATION

In this section the external port interface operation is defined.

Figure 5-1 External port write timing specification

The operation of the External port during write operations starts with the EXT\_IN\_FULL\_N signals being de-asserted by the router (at clock cycle 2 in Figure 5-1) to indicate to the external system that the router has room for more data and is ready to receive it through the External port. The External system then puts data onto the EXT\_IN\_DATA data lines and asserts EXT\_IN\_WRITE\_N to transfer data into the External port on the next rising edge of SYSCLK. As long as there is room for new data (EXT\_IN\_FULL\_N is inactive) the writer access is performed as long as EXT\_IN\_WRITE\_N is active. If no room is available the write access is ignored (cycle 9 and 10 in Figure 5-1) and will be performed when room has become available if EXT\_IN\_WRITE\_N is still active. Therefore the data (EXT\_IN\_DATA) must be valid at that time.

Figure 5-2 External port read timing specification

Reading of the External port is illustrated in Figure 5-2. When data is available in the External port FIFO then it is placed on the **EXT\_OUT\_DATA** bus and the **EXT\_OUT\_EMPTY\_N** signal is asserted to signal to the external system that data is available. This is done synchronously to the **SYSCLK** signal (e.g. clock cycle 2 in Figure 5-2). When it is ready the external system asserts the

| ANT WARMENT OF     |                  | Ref.:  | UoD_SpW-10X_                 |

|--------------------|------------------|--------|------------------------------|

| EADS<br>ASTRIUM    | SpaceWire Router |        | DataSheet                    |

| Austrian Aerospace | Data-Sheet       | Issue: | 2.0                          |

|                    |                  | Date:  | 18 <sup>th</sup> August 2006 |

**EXT\_OUT\_READ\_N** signal synchronously with the **SYSCLK** signal (e.g. clock cycle 3) and the data is then read out of the external port on the next rising edge of the **SYSCLK** (e.g. start of clock cycle 4). If there is no more data available in the FIFO then the **EXT\_OUT\_EMPTY\_N** is de-asserted once the data has been read. If the FIFO contains more data to transfer then the **EXT\_OUT\_EMPTY\_N** remains asserted, the new data is placed on the **EXT\_OUT\_DATA** bus and the external system can read it as soon as it is ready. The read access is ignored if there is no data available (**EXT\_OUT\_EMPTY\_N** is active).

# 5.2 TIME-CODE INTERFACE OPERATION

In this section the time-code interface operation is defined.

#### Figure 5-3 Time-Code Input Interface

Time-codes can be generated by the router on request of the external system to which it is attached. A time-code is generated whenever the router detects a rising edge on the. The value of the time-code to be transmitted is either taken from the inputs or from the time-code counter inside the router. The time-code source used depends on the value of the SEL\_EXT\_TIME signal when EXT\_TICK\_IN signal has a rising edge. If SEL\_EXT\_TIME is 1 then the EXT\_TIME\_IN(7:0) inputs are used to provide the contents of the time-code. If SEL\_EXT\_TIME is 0 then the internal time-code counter provides the least-significant 6-bits of the time-code and the EXT\_TIME\_IN(7:6) inputs provide the most-significant 2-bits. When using the EXT\_TIME\_IN(7:0) inputs to provide the complete time-code, the time-code is only broadcast if it is a valid time-code i.e. is one more than the internal time register of the router (see SpaceWire standard [AD1]). Note that only one router or node in a SpaceWire network should operate as a time master generating time codes (see SpaceWire standard [AD1]).

Figure 5-4 Time-Code Output Interface

When a valid time-code is received by the router the value of this time-code (flags plus time value) will be placed on the **EXT\_TIME\_OUT** outputs and the **EXT\_TICK\_OUT** signal will be set to zero. The **EXT\_TICK\_OUT** signal is set to one a short time later, once the **EXT\_TIME\_OUT** outputs have

| different of          |                  | Ref.:  | UoD_SpW-10X_                 |

|-----------------------|------------------|--------|------------------------------|

| EADS<br>ASTRIUM       | SpaceWire Router |        | DataSheet                    |

|                       | Data-Sheet       | Issue: | 2.0                          |

| () Austrian Aerospace | Data-Sheet       | Date:  | 18 <sup>th</sup> August 2006 |

|                       |                  |        |                              |

stabilised, to indicate that these outputs are valid. They then remain valid until the next time-code is received and the **EXT\_TICK\_OUT** signal will be set to zero.

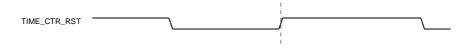

#### Figure 5-5 Time-code reset interface

When a rising edge is detected on **TIME\_CTR\_RST** then the time-code register is reset to zero.

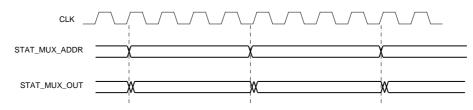

#### 5.3 ERROR/STATUS ERROR INDICATION INTERFACE OPERATION

The **STAT\_MUX\_ADDR** signal determines the output status on **STAT\_MUX\_OUT** as shown in Figure 5-6 and in Table 5-1.

Figure 5-6 Status Multiplexer output interface

When **STAT\_MUX\_ADDR** is stable **STAT\_MUX\_OUT** is output from after each clock edge.

Ref.: UoD\_SpW-10X\_

DataSheet

Issue: 2.0

🔞 Austrian Aerospace

Data-Sheet

Date: 18<sup>th</sup> August 2006

|             | Table 5-1 Mul      | tiplexed Status Pins Bit Assign | ment                    |                          |

|-------------|--------------------|---------------------------------|-------------------------|--------------------------|

| Mux Address | Status Register    | Status Signal                   | Status<br>Register Bits | Status<br>Output<br>Bits |

| 0           | Configuration Port | Packet return address error     | 1                       | 0                        |

|             |                    | Output port timeout error       | 2                       | 1                        |

|             |                    | Checksum error                  | 3                       | 2                        |

|             |                    | Packet too short error          | 4                       | 3                        |

|             |                    | Packet too long error           | 5                       | 4                        |

|             |                    | Packet EEP termination          | 6                       | 5                        |

|             |                    | Protocol byte error             | 7                       | 6                        |

|             |                    | Invalid address/data error      | 8                       | 7                        |

| 1 - 8       | SpaceWire Ports    | Packet Address Error            | 1                       | 0                        |

|             | 1 - 8 respectively | Output Port Timeout             | 2                       | 1                        |

|             |                    | Disconnect Error                | 3                       | 2                        |

|             |                    | Parity Error                    | 4                       | 3                        |

|             |                    | Escape Error                    | 5                       | 4                        |

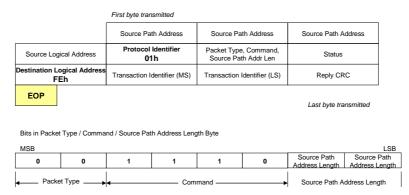

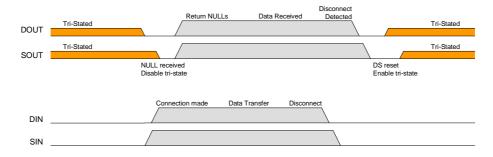

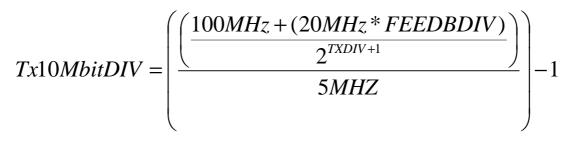

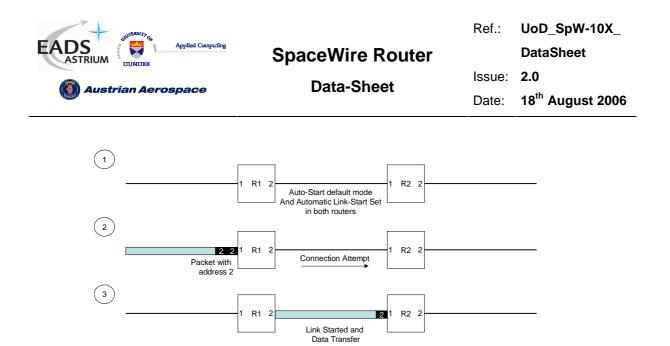

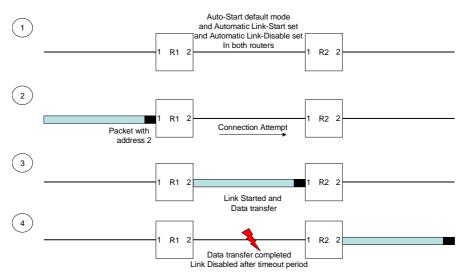

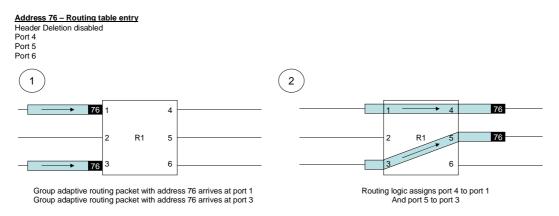

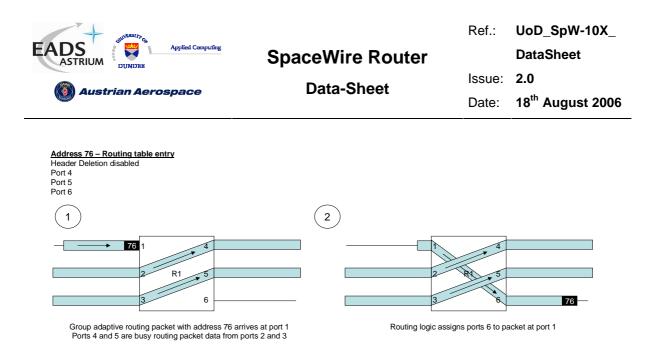

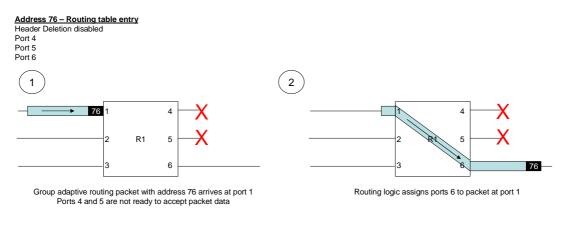

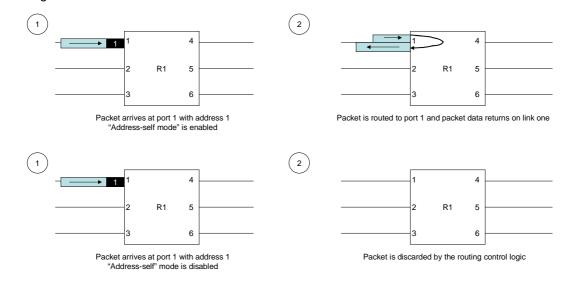

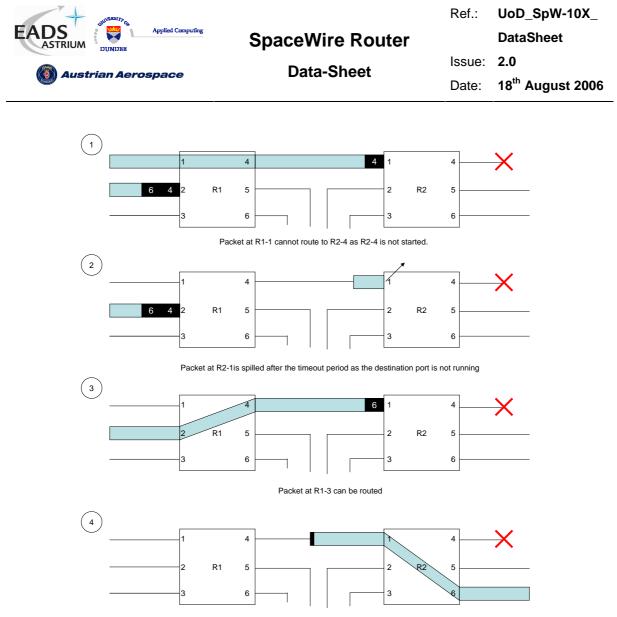

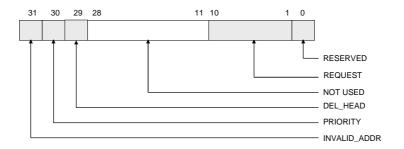

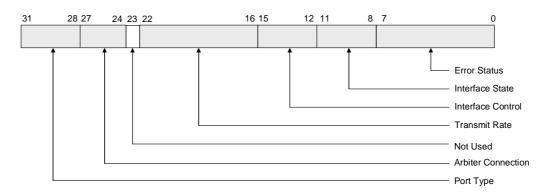

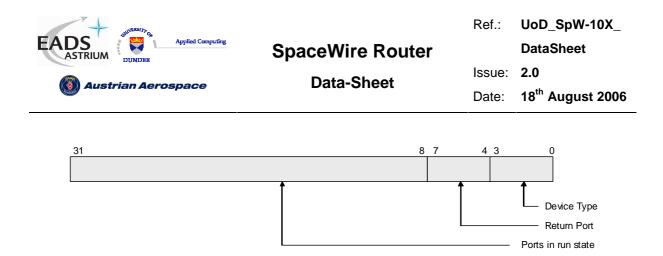

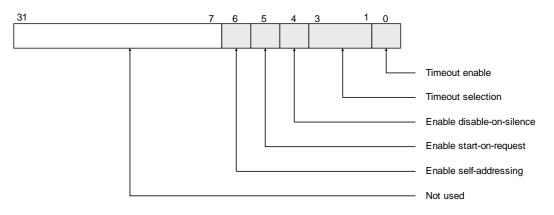

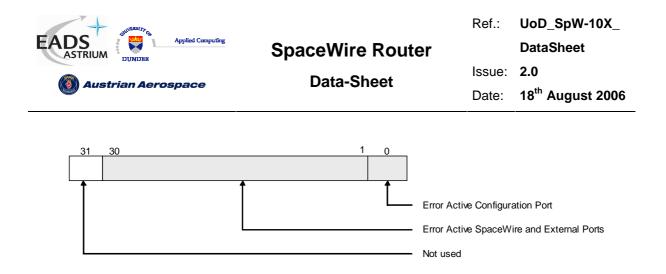

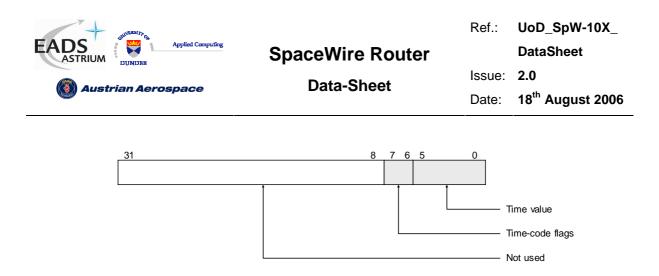

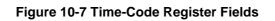

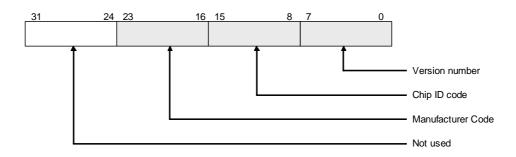

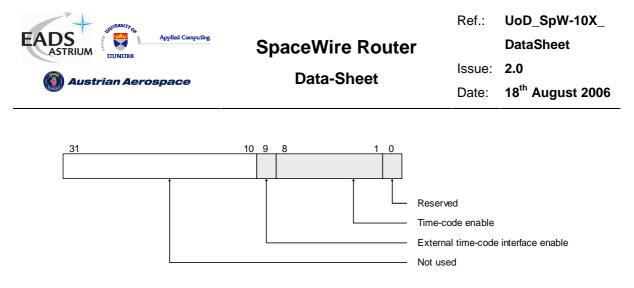

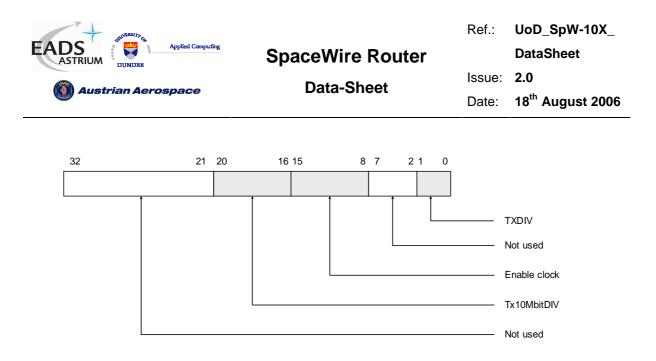

|             |                    | State A                         | 8                       | 5                        |