document title/ titre du document

# RMAP CRC Implementation

prepared by/préparé par

Albert Ferrer Florit

reference/réferenceTEC-EDP/2006.77/L Tissue/édition1revision/révision1date of issue/date d'édition25 October 2006status/étatReleasedDocument type/type de documentTechnical NoteDistribution/distribution

European Space Agency Agence spatiale européenne

page ii of iv

| Title<br>titre                   | RMAP CRC Implementa      | tion   |                                | issue 1<br>issue                  | revision<br>revision | 1 |

|----------------------------------|--------------------------|--------|--------------------------------|-----------------------------------|----------------------|---|

| author<br>auteur                 | Albert Ferrer Florit     |        |                                | date 25<br>date 20                | October<br>06        |   |

| approved by<br>approuvé by       | Luca Tunesi              |        |                                | date 25<br>date 20                | October<br>06        |   |

| reason for change                | CH /raison du changement | ANGE L | <b>DG</b><br>revision/revision | date/date                         |                      |   |

| First Issue of<br>First revision | f the document           | 1      | 0                              | 21 August 2006<br>25 October 2006 |                      |   |

Issue: 1 Revision: 1

| reason for change/raison du changement | page(s)/page(s) | paragraph(s)/paragraph(s) |

|----------------------------------------|-----------------|---------------------------|

| Forward LFSR figure was not correct.   | 3               |                           |

#### page iii of iv

## Background

CRC Galois implementation is defined by three independent configurations:

1) The polynomial that RMAP standard specifies is:  $g(x) = x^8 + x^2 + x^{1} + 1$ . There are two possible ways to represent the Galois version of the shift register (mostly called LFSR, Linear Feedback Shift Register)

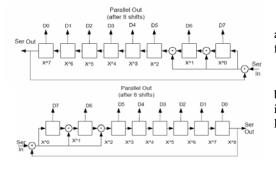

a) Use of a left register (normal or forward representation). Input bits come from the right.

b) Use of a right register. It is called reverse version because the polynomial is bit reversed in the LFSR but is the most used. Input bits come from the left.

They give the same CRC result with the output bits reversed only if the order of the input bits is the same.

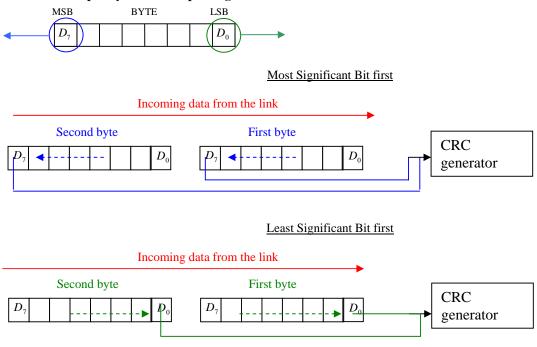

2) The first bit that enters to the LFSR can be the Least or the Most significant bit of a byte or word. **Results are completely different depending on this decision.**

Usually, because it is very intuitive, forward representation is used with the MSB being introduced first and reverse representation is used with the LSB first.

When used in communication protocols, the CRC is usually calculated in the order the bits are sent over the physical layer, to preserve the CRC's burst error detection characteristics.

3) The initial value of the shift register determines also the final CRC result.

## SpaceWire and RMAP standard:

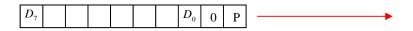

- SPW sends the LSB bit of a byte first on the link. The data character includes control (always 0) and one parity bit.

- RMAP CRC is calculated over one or more data bytes.

- ECSS-E-50-11 Draft E concerning the CRC RMAP implementation says:

### Section 6.2:

Data CRC is an 8-bit Cyclic Redundancy Check (CRC) used to confirm that the data is correct before being written in a verified write command or was correctly transferred in a non-verified write command or read reply. The data CRC starts with the byte after the header CRC and covers all the data bytes. The CRC-8 code is used which is the same as for the header CRC. CRC-8 has the following polynomial: X8 + X2 + X1 + 1, with a starting value of 00h. The Galois version of the CRC is used. VHDL and c-code implementations of this CRC algorithm are included in sub-clause 6.11, Annex A.

So, it does not say explicitly if the MSB or the LSB have to be introduced first in the shift register

### Sub-clause 6.11, Annex A:

It is classified as "(informative)" and contains a high level VHDL description that illustrates a byte-parallel implementation of the shift register or LFSR. This description assumes that the first bit processed is the MSB bit of the byte. Consequently, the C code provided generates the same results and contains a table that corresponds to the forward representation with the MSB bit being introduced first

## First RMAP CRC implementation

It uses exactly what is described in sub-clause 6.11, Annex A which is classified as "(informative)". In this annex a high level VHDL description illustrates a byte-parallel implementation of the shift register or LFSR. The important thing is that **the first bit processed is the MSB bit of the bytes.**

Other consideration is that a parallel implementation uses extra hardware resources but a slower clock than the SpW transmitter.

## Second RMAP CRC implementation

It uses a bit-serial implementation with the Galois version of the shift register. The important thing is that **the first bit introduced** in the LFSR is the LSB bit of the bytes. The rationale behind is: *The least significant bit is used first in the CRC generation algorithm as the SpaceWire protocol sends the least significant bit of a byte first on the link.* So, this implementation respects the order of the incoming bits in the transmission. This is the common choice in communication protocols in order to preserve the CRC's burst error detection characteristics.

The reverse representation is used because is the most suitable when LSB is used first.

## Conclusions

The description of the CRC algorithm in the ECSS-E-50-11 Draft E should be updated to specify which bit should be introduced first (MSB or LSB) and which polynomial representation should be used (forward or reversed).