# **SpaceWire Router (SPROUT) ASIC Features and Status**

SpaceWire Working Group Meeting, NASA/GSFC, Tuesday 15<sup>th</sup> of February 2005

**Gerald Kempf**

Austrian Aerospace GmbH

# Contents

- Features

- Performance

- Status

## SPROUT ASIC Features (1)

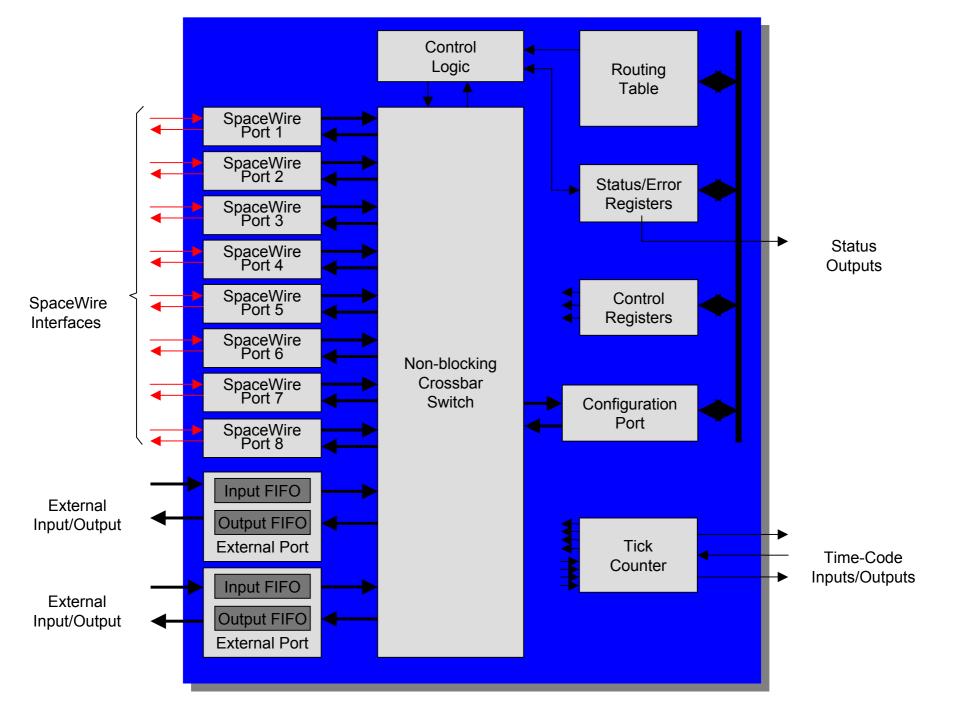

- Fully SpaceWire compliant

- Eight SpaceWire ports

- Two External (Parallel) ports

- Time-code interface

- Receiving time-codes

- Generating time-codes

- Cascadable

# SPROUT ASIC Features (2)

- Internal configuration port

- Accessible through SpaceWire or External ports

- Logical address routing table

- Control registers

- Status registers

- External pins for status/error monitoring

- External pins for start-up configuration

# SPROUT ASIC Performance (1)

## ASIC Technology

- Implementation in Atmel MH1RT gate array

- 0.35 μm CMOS process

- Radiation tolerance 100 krad(Si)

- SEU free cells up to 100 MeV cm2 / mg for all memory except a few timing critical cells in the SpaceWire interfaces

- Latch-up immunity up to 100 MeV cm2 / mg

#### Performance

- SpaceWire interface baud-rate 200 Mbits/s

- LVDS drivers/receivers with cold-sparing capability integrated on-chip

- Internal PLL with configurable output frequency to generate the SpaceWire transmitter clocks

# SPROUT ASIC Performance (2)

#### Electrical Parameters

- 4.5 W power with all links at maximum data rate

- Single 3.3 V supply voltage

- Operating temperature from -55 °C to +125 °C

- Single 30 MHz clock needed

### Package

196 pin ceramic Quad Flat Pack 25 mil pin spacing

## SPROUT ASIC Status

- FPGA Testing has been completed successfully

- SpaceWire protocol (RMAP) compatibility needs to be added

- First ASIC Prototypes are expected end of 2005

- Available directly from ATMEL as an Application Specific Standard Product

- Technical support from Star Dundee (UK)