## SpaceWire BFM for Test, Verification and Certification

#### Yuriy Sheynin

St. Petersburg State University of Aerospace Instrumentation St.Petersburg, RUSSIA

sheynin@aanet.ru

# Testing, Verification and Certification

- **Device Interoperability testing (DI);** demonstrates interoperability with a limited set of reference devices.

- Specification compliance testing (SC); demonstrates that a standard implementation complies the standard itself

## What to Test, Verify and Certify (TVC)

SpaceWire Test and Verification:

- Devices that implement SpaceWire

- SpaceWire links, link controller chips

- SpaceWire nodes

- SpaceWire routers

- IP-blocks that implement SpaceWire

- RTL-models

- Post-synthesis models

- System-level models

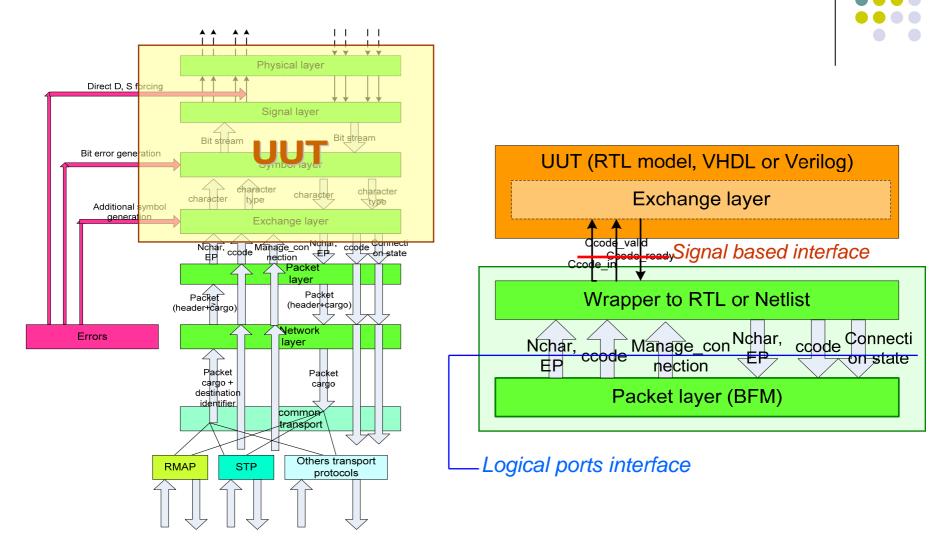

## Support for IP-blocks testing and verification

- BFM (Base Formal Model)

- hierarchical model of a protocol stack

- BFM levels correspond to the standard's protocol stack layers.

- BFM are programmed in a high-level languages (e.g. SystemC for RapidIO BFM, VHDL, Verilog)

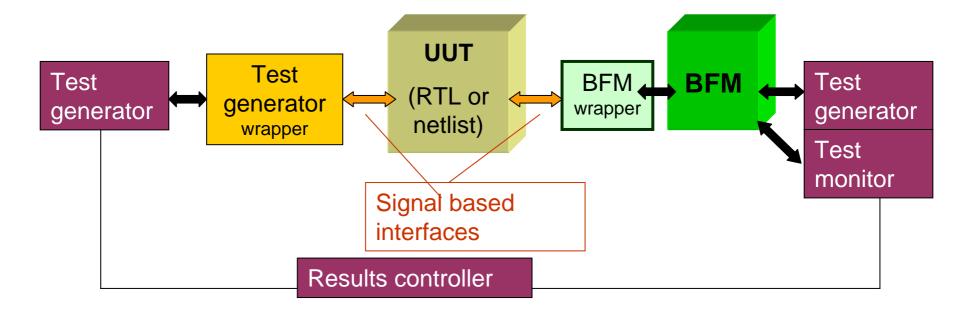

#### **Basic TVC package with a BFM**

- BFM (base formal model) of the protocol stack

- Test generator, test monitor and results controller

- BFM wrapper (to connect BFM to an RTL or netlist)

- Test generator wrapper (to connect test generator to an RTL or netlist)

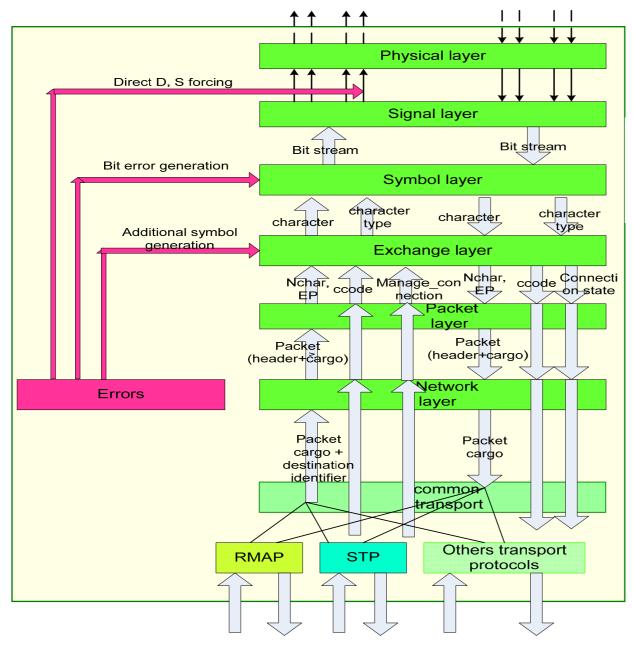

#### SpaceWire BFM Structure

•Multilayered structure

•Simulation of all correct situations

•Simulation of errors

•SystemC (VHDL, Verilog could be used)

•Works in ncSim, ModelSim, etc.

### **BFM.** Logical ports

Example of interface structure (logical ports):

int send\_Ccode(t\_code Ccode\_); bool ready\_to\_send\_Ccode();

t\_code receive\_Ccode(); bool received\_Ccode();

#### **BFM wrappers.** Working with separate layers

## **Testing with the BFM**

- IP-block (or chip) designer includes BFM modules in his testing environment, with the ready-made component models, test sequences and prescribed testing procedures

- Complement the standard test set by specific for particular UUT settings

- Runs the testing environment with his design for a sequence of standardized TVC procedures

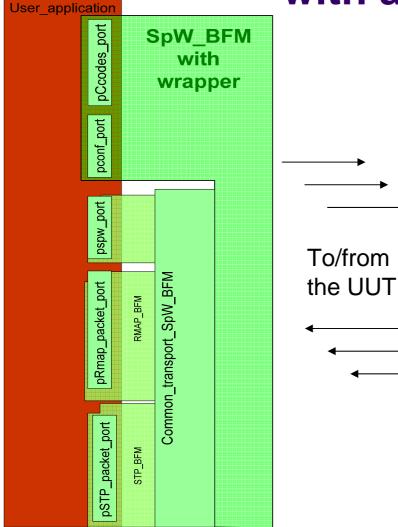

## BFM Integration with a user application

- An application integrates BFM layer classes and methods with which the testing application needs to work (Transport layer at the figure)

- The application can test sequences, send them through BFM to a UUT, receive reactions and analyse them

## **Open problems in TVC**

To be provided with the SpaceWire standard :

- Methodology for Test and Verification (informative)

- Methodology for Certification (<u>normative</u>)

- Test sets that support the methodology

- Instruments for Test, Verification and Certification

- support in development,

- an open recommended list of instruments

Thank you !