# SpaceFibre Outline Specification

Page: 1 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

Centre

University of Dundee

# SpaceFibre CODEC

# **Functional Specification**

# LIKELY TO CHANGE!

# **RESTRICTED CIRCULATION ONLY**

Prepared by: Steve Parkes

## **Chris McClements**

Martin Dunstan

Project Management: Steve Parkes

ESA Project Manager: Martin Suess

## Document Change log

| Date                          | Revision No | Comments | Change Author |  |  |

|-------------------------------|-------------|----------|---------------|--|--|

| 31 <sup>st</sup> October 2007 | Draft A     | Initial  | Steve Parkes  |  |  |

|                               |             |          |               |  |  |

|                               |             |          |               |  |  |

|                               |             |          |               |  |  |

|                               |             |          |               |  |  |

Page: 3 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

# Outline Specification

## Contents

| 1.    | INTRODUCTION                             | 9  |

|-------|------------------------------------------|----|

| 1.1   | OVERVIEW                                 | 9  |

| 1.2   | TERMS AND DEFINITIONS                    | 9  |

| 1.2.  | 1 List of abbreviations                  | 9  |

| •     |                                          |    |

| 2.    | SPACEFIBRE CODEC ARCHITECTURAL OVERVIEW  | 11 |

| 2.1   | ARCHITECTURE                             |    |

| 2.1.  |                                          |    |

| 2.1.2 | 2 EMC Mitigation                         | 14 |

| 2.1.3 | 3 Framing                                | 15 |

| 2.1.4 |                                          |    |

| 2.1.  | 5 Data rate adjustment                   | 15 |

| 2.1.6 | 8 8B/10B encoding and decoding           | 16 |

| 2.1.  | 7 Symbol and ordered set synchronisation | 16 |

| 2.1.8 |                                          |    |

| 2.1.9 | 9 Line driver and receiver               | 16 |

| 2.2   | TYPICAL OPERATION                        | 17 |

| 3.    | OUTLINE SPECIFICATIONS                   | 19 |

| 3.1   | DATA SCRAMBLING                          | 19 |

| 3.2   | 8B/10B ENCODING AND DECODING             | 20 |

| 3.2.  | 1 8B/10B Encoding                        | 22 |

| 3.2.2 | 2 8B/10B Decoding                        | 23 |

| 3.3   | SERIALISATION AND DE-SERIALISATION       | 28 |

| 3.4   | RECEIVE CLOCK RECOVERY                   | 28 |

| 3.5   | CHARACTER SYNCHRONISATION                | 29 |

| 3.6   | RECEIVE ELASTIC BUFFER                   | 31 |

| 3.7   | RECEIVE SYNCHRONISATION STATE MACHINE    | 34 |

| 3.8   | LINK STATE MACHINE                       | 36 |

| 3.9   | LINK INITIALISATION                      | 38 |

**Outline Specification**

Page: 4 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

| 3.10   | LINK INITIALISATION SEQUENCE DIAGRAMS    | .41 |

|--------|------------------------------------------|-----|

| 3.10.1 | Initialisation from AutoStart            | .41 |

| 3.10.2 | Initialisation when both ends Link Start | .43 |

| 3.10.3 | Initialisation with Speed Change         | .45 |

| 3.10.4 | Re-Initialisation following Loss-of-Sync | .45 |

| 3.11   | POLARITY CHANGE                          | .46 |

| 3.11.1 | The Need for Polarity Change             | .46 |

| 3.11.2 | Polarity Detection                       | .47 |

| 3.11.3 | Changing Polarity                        | .48 |

| 3.12   | LINK ERROR RECOVERY                      | .48 |

| 3.13   | POWER MANAGEMENT                         | .49 |

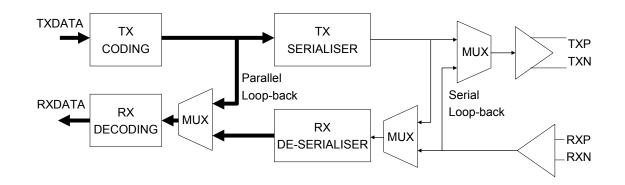

| 3.14   | LOOP-BACK                                | .49 |

| 4. SF  | PACEFIBRE SPECIFICATION                  | .51 |

| 4.1 II | NTERFACE SPECIFICATION                   | .51 |

| 4.1.1  | User Interface                           | .51 |

| 4.1.2  | Data Interface                           | .53 |

| 4.1.3  | SerDes Interface                         | .54 |

| 4.1.4  | Serial Interface                         | .56 |

| 4.2 F  | UNCTIONAL SPECIFICATION                  | .57 |

| 4.2.1  | Data Words and Characters                | .57 |

| 4.2.2  | Ordered Sets                             | .57 |

| 4.2.3  | Data Framing                             | .61 |

| 4.2.4  | Scrambling/ Descrambling                 | .62 |

| 4.2.5  | Ordered Set Injection                    | .64 |

| 4.2.6  | Link Initialisation and Power Management | .64 |

| 4.2.7  | Data Rate Adjustment                     | .77 |

| 4.2.8  | 8B/10B Encoding/Decoding                 | .78 |

| 4.2.9  | Serialiser/Deserialiser                  | .79 |

| 4.2.10 | Synchronisation                          |     |

| 4.2.11 | Inversion                                |     |

| 4.2.12 | Electrical SpaceFibre Medium             |     |

| 4.2.13 | Fibre Optic Driver and Receiver          |     |

| 4.2.14 | Parallel Loopback                        |     |

| 4.2.15 | Serial Loopback                          | .86 |

| 5.  | SPACEFIBRE FLOW CONTROL AND VIRTUAL CHANNELS | .87 |

|-----|----------------------------------------------|-----|

| 5.1 | VIRTUAL CHANNELS                             | .87 |

| 5.2 | FLOW CONTROL                                 | .87 |

Page: 6 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

# Outline Specification

## List of Tables

| TABLE 3-1 5B/6B ENCODING.                           |    |

|-----------------------------------------------------|----|

| TABLE 3-2 3B/4B ENCODING                            |    |

| TABLE 3-3 8B/10B CONTROL (K) CODES                  |    |

| TABLE 3-4 DETECTION OF ERROR BY INVALID CODE        |    |

| TABLE 3-5 DETECTION OF ERROR BY INVALID DISPARITY   |    |

| TABLE 4-1 TRANSMIT DATA FRAME INTERFACE             |    |

| TABLE 4-2 TRANSMIT ORDERED SET INTERFACE            |    |

| TABLE 4-3 RECEIVE DATA FRAME INTERFACE              |    |

| TABLE 4-4 RECEIVE ORDERED SET INTERFACE             |    |

| TABLE 4-5 TRANSMIT DATA INTERFACE                   |    |

| TABLE 4-6 RECEIVE DATA INTERFACE                    |    |

| TABLE 4-7 TRANSMIT SERDES INTERFACE (10-BIT)        | 55 |

| TABLE 4-8 TRANSMIT SERDES INTERFACE (20-BIT)        |    |

| TABLE 4-9 TRANSMIT SERDES INTERFACE (40-BIT)        |    |

| TABLE 4-10 RECEIVE SERDES INTERFACE (10-BIT)        |    |

| TABLE 4-11 RECEIVE SERDES INTERFACE (20-BIT)        | 56 |

| TABLE 4-12 RECEIVE SERDES INTERFACE (40-BIT)        |    |

| TABLE 4-13 TRANSMIT SERIAL OUTPUT                   |    |

| TABLE 4-14 RECEIVER SERIAL INPUT                    | 57 |

| TABLE 4-15: LINK LAYER ORDERED SETS                 |    |

| TABLE 4-16: POWER MANAGEMENT AND RESET ORDERED SETS | 59 |

| TABLE 4-17: DATA FRAMING ORDERED SETS               | 60 |

| TABLE 4-18: FLOW CONTROL ORDERED SET.               | 60 |

| TABLE 4-19 COLDRESET STATE                          |    |

| TABLE 4-20 WARMRESET STATE                          | 67 |

| TABLE 4-21 AUTOSTART STATE                          |    |

| TABLE 4-22 NOTCONNECTED STATE                       |    |

| TABLE 4-23 NEARENDCONNECTED STATE                   |    |

| TABLE 4-24 FARENDCONNECTED STATE                    |    |

| TABLE 4-25 CONNECTED STATE                          |    |

| TABLE 4-26 ACTIVE STATE                             |    |

| TABLE 4-27 CHANGINGPOLARITY STATE                   |    |

| TABLE 4-28 CHANGINGSPEED STATE                      |    |

| TABLE 4-29 FAILEDINIT STATE                         |    |

| TABLE 4-30 BITSYNC STATE                            |    |

| TABLE 4-31 SYMBOLSYNC STATE | 83 |

|-----------------------------|----|

| TABLE 4-32 CHECKSYNC STATE  | 84 |

| TABLE 4-33 READY STATE      | 85 |

Page: 8 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

## **Outline Specification**

## List of Figures

| FIGURE 2-1 OVERVIEW OF SPACEFIBRE CODEC                                | 12 |

|------------------------------------------------------------------------|----|

| FIGURE 2-2 SPACEFIBRE CODEC ARCHITECTURE                               | 13 |

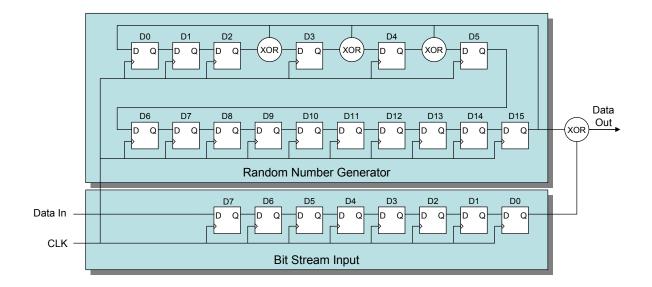

| FIGURE 3-1 SCRAMBLER / DE-SCRAMBLER                                    | 20 |

| FIGURE 3-2 8B/10B ENCODER                                              | 22 |

| FIGURE 3-3 8B/10B NOTATION                                             | 25 |

| FIGURE 3-4 TYPICAL PHASE-LOCKED LOOP                                   | 28 |

| FIGURE 3-5 CHARACTER SYNCHRONISATION USING A PLUS COMMA                | 29 |

| FIGURE 3-6 CHARACTER ALIGNMENT AFTER DE-SERIALISATION                  | 30 |

| FIGURE 3-7 CHARACTER ALIGNMENT DURING DE-SERIALISATION                 | 31 |

| FIGURE 3-8 RECEIVE ELASTIC BUFFER - NOMINAL CONDITION                  | 32 |

| FIGURE 3-9 RECEIVE ELASTIC BUFFER EMPTYING                             | 32 |

| FIGURE 3-10 RECEIVE ELASTIC BUFFER FILLING UP                          | 33 |

| FIGURE 3-12 RECEIVE SYNCHRONISATION STATE MACHINE                      | 35 |

| FIGURE 3-13 LINK STATE MACHINE                                         | 37 |

| FIGURE 3-14 LINK INITIALISATION STATE MACHINE                          | 39 |

| FIGURE 3-15: INITIALISATION FROM AUTO-START                            | 42 |

| FIGURE 3-16: INITIALISATION FROM AUTO-START THROUGH FARCONNECTED STATE | 43 |

| FIGURE 3-17: INITIALISATION WHEN BOTH ENDS LINK START                  | 44 |

| FIGURE 3-18: INITIALISATION THROUGH FARCONNECTED STATE                 | 44 |

| FIGURE 3-19: INITIALISATION WITH SPEED CHANGE                          | 45 |

| FIGURE 3-20: RE-INITIALISATION AFTER LOSS OF SYNC                      | 46 |

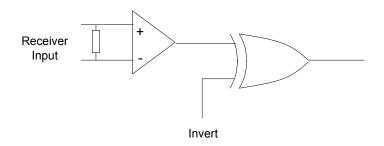

| FIGURE 3-21: INVERSION OF RECEIVER INPUT                               | 48 |

| FIGURE 3-22 LOOP-BACK FACILITIES                                       | 50 |

| FIGURE 4-1 DATA FRAME FORMAT                                           | 61 |

| FIGURE 4-2 IDLE FRAME FORMAT                                           | 62 |

| FIGURE 4-3 SCRAMBLER / DE-SCRAMBLER                                    | 63 |

| FIGURE 4-4 LINK INITIALISATION STATE MACHINE                           | 65 |

| FIGURE 4-5 RECEIVE SYNCHRONISATION STATE MACHINE                       | 81 |

|                                                                        |    |

Page: 9 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

### 1. INTRODUCTION

#### 1.1 OVERVIEW

This document provides an outline specification for the SpaceFibre CODEC.

This document begins, in Section 2, with an overview of the architecture of the SpaceFibre CODEC and a brief description of how it operates. Section 3 then describes each part of the CODEC in turn. The concepts behind each part are described giving a rationale for the design decisions made. The specification for SpaceFibre is provide in section 4, with section 4.1 providing the interface specification and section 4.2 the functional specification. Section 5 provides an overview of the virtual channel and flow control mechanisms that will be used with the SpaceFibre CODEC.

#### 1.2 TERMS AND DEFINITIONS

#### 1.2.1 List of abbreviations

- 8B/10B 8-bit to 10-bit

- AC Alternating Current

- AD Applicable Document

- ASIC Application Specific Integrated Circuit

- CODEC Coder/Decoder

- CML Current Mode Logic

- D/K Data/Control

- ECSS European Cooperation for Space Standardization

- EDAC Error Detection and Correction

- EEP Error End of Packet

- EM Electro-Magnetic

- EMC Electro-Magnetic Compatibility

- EOF End Of Frame

- EOP End Of Packet

Page: 10 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

- ESA European Space Agency

- FCT Flow Control Token

- FIFO First In First Out

- FPGA Field Programmable Gate Array

- GAR Group Adaptive Routing

- LSB Least Significant Bit

- LVDS Low Voltage Differential Signalling

- MSB Most Significant Bit

- OS Ordered Set

- PCI Peripheral Component Interconnect

- PLL Phase-Locked Loop

- SEU Single Event Upset

- SOF Start Of Frame

- SOW Statement of Work

- TDA to be advised

- TBC to be confirmed

- TBD to be defined

- UoD University of Dundee

- VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language

### 2. SPACEFIBRE CODEC ARCHITECTURAL OVERVIEW

This section provides an overview of the SpaceFibre CODEC architecture and describes how it operates.

#### 2.1 ARCHITECTURE

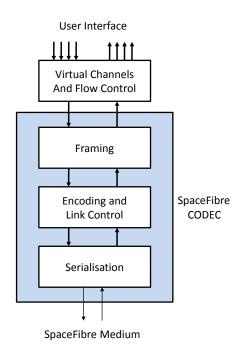

An overview of the SpaceFibre CODEC architecture is provided in

There are four main functional blocks:

- Virtual Channel and Flow Control: responsible for quality of service channel and flow control over the SpaceFibre link.

- Framing: responsible for framing data to be sent over the SpaceFibre link and for inserting user ordered sets within the data stream.

- Encoding and Link Control: responsible for encoding data into symbols for transmission and vice versa for reception and for initialising the link.

- Serialisation: responsible for serialising and de-serialising SpaceFibre symbols so that they may be transferred over the fibre optic or copper medium.

The latter three blocks form the SpaceFibre CODEC.

**Outline Specification**

Page: 12 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 2-1 Overview of SpaceFibre CODEC

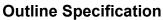

The detailed architecture of the SpaceFibre CODEC is illustrated in Figure 2-2.

The SpaceFibre CODEC is split into several functional layers:

- User interface

- EMC mitigation

- Framing

- Link initialisation and power management

- Data rate adjustment

- 8B/10B encoding and decoding

- Parallel loop-back

- Symbol and ordered set synchronisation

- Serialisation and de-serialisation

- Serial loop-back

- Line driver and receiver

Page: 13 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

Figure 2-2 SpaceFibre CODEC Architecture

Page: 14 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### 2.1.1 User Interface

The user interface comprises four independent interfaces for sending and receiving data frames and user ordered sets. A user ordered set comprises a four symbol code: starting with a comma and followed by three other symbols either data or K-codes. The user ordered sets will be defined in a higher layer of SpaceFibre and must not conflict with the ordered sets used within the link layer. User order sets support services like time-code and interrupt distribution. A data frame is a series of 32-bit data words (4 bytes) delimited by a start of frame (SOF) and end of frame (EOF). The data frame is limited to a maximum frame size which will be specified by the SpaceFibre standard. Data frames are transferred rather that individual bytes or words of data because it enables handshaking at the user interface to be done much more slowly at the boundaries of the frames rather than on each byte or word boundary.

#### 2.1.2 EMC Mitigation

Sending a constant bit pattern over a serial link can cause high levels of EM emission due to the energy being concentrated in a few frequency components. To avoid this data may be scrambled before transmission by multiplying the data sequence by a pseudo-random sequence. A pseudo-random sequence approximates white noise and thus has a wide bandwidth. Multiplication of the data by the pseudo-random sequence broadens the frequency components, spreading the energy and reducing the peak emission levels.

SpaceFibre uses this technique to mitigate the EM emissions over copper SpaceFibre links. A scrambler is used to scramble the data in each data frame. The original data is then recovered by a de-scrambler at the other end of the link. To help with this process each frame is multiplied by the same pseudo-random sequence i.e. the pseudo-random generator is re-seeded with the same seed at the start of each frame. Ordered sets are not scrambled.

When the link has no other data to send it will send IDLE ordered sets to keep the link active. Sending repeated IDLEs will once again result in excessive EM emission spectral spikes. To avoid this whenever there are no data frames to send an idle frame comprising all zero data is automatically generated. The idle frame is scrambled in the same way as normal data frames, reducing the EM emissions. Idle frames can be terminated, with an EOF, as soon as another data frame becomes ready for transmission, so that the introduction of idle frames does not significantly affect the sending of data frames.

Page: 15 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

### 2.1.3 Framing

Framing is the delimiting of data and idle frames by start of frame (SOF) and end of frame (EOF) ordered sets. There are two types of start of frame: start of data frame (SDF) and start of idle frame (SIF), and also two types of end of frame: normal end of frame (EOF) and error end of frame (EEF) which is used when some error is the transmitting system has caused a data frame to be terminated prematurely.

#### 2.1.4 Link initialisation and power management

Link initialisation and power management is handled by a link state machine. In the current study power management is not considered any further.

The link initialisation state machine is responsible for initialising the link prior to transfer of data frames, idle frames or user ordered sets. During link initialisation bit synchronisation, symbol synchronisation and ordered set synchronisation are performed. A handshake protocol is used to ensure that both ends of the link have achieved synchronisation. Speed negotiation is also performed during initialisation.

#### 2.1.5 Data rate adjustment

The two ends of the link operate at the same bit rate within the limits of the crystal oscillators at either end. This is nominally 2.5 Gbits/s  $\pm$  100 ppm for a typical crystal oscillator. An elastic-buffer is used in the receiver to compensate for any difference in the clocks at either end of the link. If the transmitter is operating very slightly faster than the receiver then the receive elastic-buffer will start to fill up. If the transmitter is running more slowly than the receiver then the receive elastic-buffer will start to empty. Ideally the receive elastic-buffer should be kept half full. To do this the transmitter sends SKIP ordered sets periodically, at least every 5000 ordered sets. If the receive elastic-buffer is in more than half full then the SKIP ordered set is skipped over when reading out of the buffer *i.e.* is ignored and the ordered set or data following is read out instead. This has then effect of reading out two ordered sets rather than one so the buffer becomes emptier. If the receive elastic-buffer is less than half full then the SKIP ordered set is read out but the buffer output pointer is not updated so that the SKIP is read out twice. This slows down the emptying of the receive elastic-buffer and make the buffer fuller.

The receive elastic-buffer is an important element in the SpaceFibre CODEC: it allows data or ordered sets to be read out of the 8B/10B encoder every cycle without having to do a hand-shake to see if a character is ready to be read. This dramatically improves the speed of operation of the interface. Handshaking is done at a higher level, handshaking for complete data frames to reduce handshake overhead.

#### 2.1.6 8B/10B encoding and decoding

The 8B/10B encoding takes an 8-bit input together with a data/control (D/K) flag and provides a 10-bit code for serialisation. The 8B/10B decoder does the inverse operation to recover the 8-bit value and D/K flag. The 8B/10B encoding/decoding is described further in section 3.2.

#### 2.1.7 Symbol and ordered set synchronisation

In the receiver once the bit synchronisation has been achieved and the bit stream recovered (see sections 2.1.8 and 3.4) it is necessary to determine the boundary of the symbols in the bit stream (every 10-bits) and then to identify the ordered set and data set boundary (every 40-bits). The comma symbol (see section 3.2) is used to support both symbol and ordered/data set boundary detection. The comma symbol contains a unique 7-bit code which can be used to detect the boundary between the comma symbol and the next symbol. Ordered sets begin with a comma symbol so the boundary between ordered/data sets can also be detected using the comma symbol.

Ordered sets will be carefully defined so that pairs of ordered sets sent during link initialisation (INITs) and during normal link operation (SKIPs) contain both plus and minus commas. This is to enable the protocol to work with interfaces which only recognise one type of comma.

#### NOTE: SKIPs and INITs might not have this property yet!

#### 2.1.8 Serialisation and de-serialisation

Serialisation is the conversion of the 10-bit parallel symbols to a bit stream.

De-serialisation is the recovery of a 10-bit parallel stream from a serial bit stream. This requires clock recover from the bit stream using a phase-locked loop (PLL) which is helped by the 8B/10B code giving a transition rich set of transmitted codes.

#### 2.1.9 Line driver and receiver

The serialised data is driven onto a 100 ohm differential impedance line using current-mode logic (CML). This may then be used to drive a fibre optic transmitter. A fibre optic receiver converts the received optical signals back to CML which is then passed over a 100 ohm differential impedance line to the receiver. Both the CML driver and CML receiver are AC coupled to provide galvanic isolation.

CML may be used on its own to provide a copper interface to SpaceFibre.

Page: 17 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

## 2.2 TYPICAL OPERATION

The typical operation of the SpaceFibre interface will now be described with reference to Figure 2-2.

Data frames (TX\_DATA\_FRAME) are passed into the CODEC for transmission. The data is scrambled by the Scrambler to reduce EM emissions from repeating data patterns. If there is no data frame to send an idle frame, containing all zeros, is generated automatically to fill the gap in the data. SOF and EOF are added to the scrambled data to delimit one frame from the next. User ordered sets may be sent at any time taking priority over data being sent. User ordered sets may appear at any point within a data frame.

During link initialisation or link initialisation ordered sets (INIT\_1 and INIT\_2) are multiplexed into the transmitter to perform the initialisation handshake and configuration under direction of the Link Initialisation state machine. Power management ordered sets are also injected into the data stream at this point but this is outside the scope of the current study.

To support the receive elastic-buffer skip ordered sets are injected into the transmit data stream at a rate determined by the Skip Counter and at an interval no longer than 5000 ordered sets (see section 3.6). Idle ordered sets are sent when the transmitter is in the Active state and there is no other information to send.

The 8B/10B encoder encodes the 8-bit data plus data/control (D/K) flag into a 10-bit code, which has special properties to support data transfer and recovery in the receiver (see section 3.2). The data sets and ordered sets are four symbols wide so four parallel 8B/10B encoders are required to perform the encoding. Alternatively one 8B/10B encoder operating at four times the data/ordered set rate may be used. The 10-bit code from the 8B/10B encoder is passed to the serialiser which converts it into a serial bit stream. This bit stream is driven on to the communications medium by the driver.

The receiver takes the incoming bit stream and recovers the bit stream clock using a phase locked loop. The recovered bit clock is used by the de-serialiser to convert the serial bit stream into a slower speed, parallel data stream which can be handled a little more easily. The 10-bit symbols are separated from the parallel data stream by the symbol and ordered set synchronisation unit. This unit determines the position of comma codes in the 10-bit parallel data stream and then outputs the data correctly aligned on the data set and ordered set boundaries. At this point the data set and ordered sets are 40-bits wide: sets of four 10-bit symbols. The ordered sets all start with a comma symbol..

The 40-bit data is passed to a set of four 8B/10B encoders which decode each 10-bit symbol to 8-bits plus D/K flag. The 8B/10B decoder is run from the received clock. The 8B/10B decoder detects various forms of error: invalid 10-bit code and incorrect running disparity. A receive synchronisation state machine monitors the operation of the Symbol and OS Synchronisation unit and the 8B/10B decoders and determines when the receiver is synchronised or has lost sync.

The set of four decoded symbols are buffered in the receive elastic-buffer, which copes with any differences between the receive clock and the local system clock (see section 3.6).

The output from the receive elastic-buffer is filtered for SKIP, IDLE and Initialisation ordered sets. SKIP and IDLE ordered sets are discarded and initialisation ordered sets are passed to the Link Initialisation state machine. User ordered sets are separated from the data frames and passed to the RX\_ORD\_SET interface. The SOF and EOF markers are checked and stripped from the data frame. The data is passed up to the de-scrambler, which unravels the scrambled data to reveal the original data. The unscrambled data is then passed to the RX\_DATA\_FRAME interface. Idle frames are disposed of.

Two loop-back facilities are provided inside the CODEC for test purposes. The first provides loop-back of the parallel 10-bit codes and the second loops-back the serial data before it is driven onto the physical medium. The serial loop-back provides both local and remote loop back, *i.e.* serial data being sent is looped back into the receive de-serialiser and the bit stream data being received is fed back to the line driver.

The Link Initialisation state machine provides support for link initialisation and recovery from errors. During initialisation it ensures that bit and character synchronisations are achieved and that the two ends of the link are both ready to send and receive data.

#### 3. OUTLINE SPECIFICATIONS

This section provides an outline specification for the SpaceFibre CODEC. It considers each function within the CODEC in turn, providing a rationale for the design decisions made and then provides an outline specification.

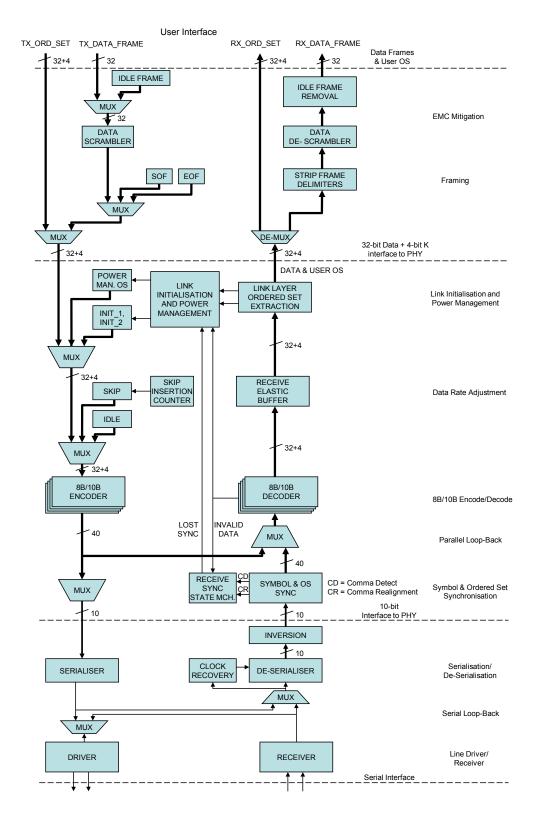

#### 3.1 DATA SCRAMBLING

Data scrambling is a technique used to reduce the electro-magnetic (EM) emissions from a communications system. The data signal is convolved with a wideband signal which results in the spectrum of the data being broadened. Possible peaks in the EM spectrum of the original data signal are spread out reducing the energy at any single frequency.

A random number generator is used to produce the wideband signal which is XORed with the data being transmitted. At the beginning of each frame being transmitted the random number generator is reseeded with a specific value. A similar random number generator in the receiver, seeded with the same seed as in the transmitter at the start of every new frame, is used to de-scramble the data. The incoming data is XORed with the random number sequence to reveal the original data stream.

The random number generator is implemented using a linear feedback shift register as shown in Figure 3-1. The scrambling/de-scrambling polynomial used is the same as that used in PCI-Express:

$G(x) = X^{16} + X^5 + X^4 + X^3 + 1$

The seed for the random number generator is FFFF<sub>h</sub> *i.e.* all flip-flops in the random number generator are set to 1.

# SpaceFibre Outline Specification

Page: 20 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 3-1 Scrambler / De-Scrambler

#### 3.2 8B/10B ENCODING AND DECODING

8B/10B encoding encodes 8-bit data bytes into 10-bit characters for transmission. The 8B/10B encoding has several advantages over direct 8-bit transmission.

- 1. It provides a transmitted data stream with roughly the same number of 1's as 0's giving the data a zero DC bias, improving the transmission characteristics and enabling AC coupling.

- 2. Since a 10-bit code has 1024 possible values and not all of these are needed to send an 8-bit value there are spare valid codes left over that can be used for control codes.

- 3. It guarantees that there will be sufficient number of bit transitions in the serial data stream to enable the recovery of the bit clock using a phase-locked loop. A maximum of five consecutive ones or zeros are ensured with 8B/10B encoding.

- 4. Since all characters, both data and control characters, are transmitted with 10-bits the bit and character transmission rates are constant simplifying the transmission and reception of characters. This is in contrast to SpaceWire where four different code lengths are possible: 4-bit for control codes, 8-bits for Null, 10-bits for data and 14-bits for time-codes which complicates character transmission and reception.

- 5. Codes that are unused by the 8B/10B encoding can be used to detect link errors *i.e.* if an unused code occurs then there has been a transmission error.

To avoid significant DC components 8B/10B encoding uses only the 10-bit codes that contain either 5 ones and 5 zeros, 6 ones and 4 zeros, or 4 ones and 6 zeros. There are enough of these to encode the 8-bit data byte and several possible control codes. Characters encoded with 5 ones and 5 zeros

Page: 21 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

have neutral disparity and will produce zero DC bias. However, if a sequence of bytes was transmitted that contained characters all with 6 ones and 4 zeros the DC component would slowly increase. A similar opposite effect would occur if the characters all contained 4 ones and 6 zeros. To prevent this increasing DC bias and to maintain an equal number of transmitted ones and zeros each character with an unequal number of ones and zeros has two possible codes one with 6 ones and 4 zeros and the other with 4 ones and 6 zeros.

Every time the transmitter sends a character with 6 ones and 4 zeros it will record the fact that it has sent more ones than zeros and the next time it has to send a character with an uneven number of bits it will choose the code that has 4 ones and 6 zeros. This keeps the average number of ones and zeros the same and eliminates any DC bias in the transmitted signal. The Current Running Disparity variable is set to one (positive) when more ones have been sent than zeros and to zero (negative) when more zeros have been sent than ones. Characters with 5 ones and 5 zeros have neutral disparity and do not affect the Current Running Disparity value. When a character with an unequal number of ones and zeros is to be sent, the value of the Current Running Disparity will determine which of the two possible 10-bit codes will be sent. If the Current Running Disparity is positive then the option with 4 ones and 6 zeros is sent, if it is negative then the other option with 6 ones and 4 zeros is transmitted.

Once all 256 possible values of an 8-bit data byte have been assigned a code with 5 ones and 5 zeros or a pair of codes with unequal numbers of ones and zeros, there are just 12 valid codes left out of the possible 1024 values of a 10-bit code. The others have more than six ones or more than six zeros and are invalid.

## 3.2.1 8B/10B Encoding

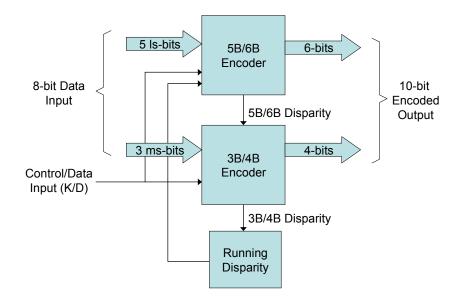

8B/10B encoding is normally done using a pair of look-up tables as shown in Figure 3-2 rather than a single look-up table.

Figure 3-2 8B/10B Encoder

The five least-significant bits are encoded first using a 5B/6B encoder. This takes into account whether the 5 least significant bits are part of a control or data word as determined by the K/D input and also the current running disparity of the link. The 5B/6B encoding table is given in Table 3-1. This table has the following properties:

- The six bit outputs consist of either three ones and three zeros, four ones and two zeros or two ones and four zeros.

- When the output code has neutral disparity (three ones and three zeros) there is one code independent of the running disparity (except for D07.y which has two codes based on the running disparity). The complement of a neutral disparity code also has neutral disparity and, except for D07.y, corresponds to a different input symbol. By definition, using a neutral disparity code will not affect the running disparity.

- When the output code has non-neutral disparity (four ones and two zeros or two ones and four zeros) there are two alternative codes provided which are the complement of each other. The code that is applied when the current running disparity of the link is negative (-ve) has four ones and two zeros which will then make the disparity out of the 5B/6B encoder positive. Similarly when the current running disparity is positive (+ve) the code with two ones and four zeros is applied making the 5B/6B disparity negative.

Page: 23 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

• The coding table is organised to minimise the amount of logic needed to implement it so that wherever possible there is a one to one mapping of bits from the 5-bit input to the 6-bit output. Note that K28.y must be treated as a special case.

The six-bit output of the 5B/6B encoder forms the six least-significant bits of the 8B/10B encoder output. The 5B/6B disparity is used in the encoding of the three most-significant bits of the 8-bit input data. The 5B/6B disparity, three most significant bits of the input data and the control/data flag (K/D) are fed into a separate 3B/4B encoder which produces the four most significant bits of the 8B/10B encoder output and a new value for the running disparity. The contents of the 3B/4B encoding table are given in Table 3-2. This table has the following properties:

- Only 12 possible codes are valid, those shown in the Table 3-3.

- When the output code has non-neutral disparity there are two codes which are the complement of each other (with the exception of the codes for Dxx.7). One of these two codes will be used depending on the 5B/6B disparity. If the 5B/6B disparity is negative then the option with three ones and one zero will be used resulting in an overall positive disparity which will be the new value of the running disparity. The opposite is the case when the 5B/6B disparity is positive.

- The encoding for Dxx.7 has an alternative coding to prevent five consecutive ones being transmitted. The -ve current running disparity alternative (0111<sub>b</sub>) is used for D17.7, D18.7 and D20.7. The +ve current running disparity alternative (1000<sub>b</sub>) is used for D11.7, D13.7 and D14.7. This does complicate the encoding somewhat because these special cases have to be identified in the input data stream and the alternative code activated.

The complete 8B/10B encoding is performed by combining the results of the 5B/6B and 3B/4B encoding steps.

#### 3.2.2 8B/10B Decoding

The task of decoding 8B/10B symbols is more complicated than the encoding process since a large number of input codes are mapped to a few valid output codes. Care must be taken to ensure that invalid 8B/10B codes are not accidentally considered to be valid simply because the 5B/6B and 3B/4B components are individually valid. An example is  $1110101110_{b}$  which has a valid 5B/6B component  $111010_{b}$  (-D23.y) and a valid 3B/4B component  $1110_{b}$  (Dxx.7 normal encoding). This is invalid because the alternative Dxx.7 encoding  $0111_{b}$  encoding ought to have been used.

Additional care must be taken with the 3B/4B decoder since the 4-bit input cannot distinguish between K and D codes. For example,  $0110_b$  represents either -Kxx.1, or Dxx.6 or +Kxx.6.

## **Outline Specification**

Page: 24 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

| Table 3-1 5B/6B Encoding |                            |                                            |                                            |  |  |

|--------------------------|----------------------------|--------------------------------------------|--------------------------------------------|--|--|

| Input Output             |                            |                                            |                                            |  |  |

| Data Input               | Data bits 43210<br>(EDCBA) | Current Running<br>Disparity -ve<br>abcdei | Current Running<br>Disparity +ve<br>abcdei |  |  |

| D00.y                    | 00000                      | 100111                                     | 011000                                     |  |  |

| D01.y                    | 00001                      | 011101                                     | 100010                                     |  |  |

| D02.y                    | 00010                      | 101101                                     | 010010                                     |  |  |

| D03.y                    | 00011                      | 110                                        | 001                                        |  |  |

| D04.y                    | 00100                      | 110101                                     | 001010                                     |  |  |

| D05.y                    | 00101                      | 101                                        | 001                                        |  |  |

| D06.y                    | 00110                      | 011                                        | 001                                        |  |  |

| D07.y                    | 00111                      | 111000                                     | 000111                                     |  |  |

| D08.y                    | 01000                      | 111001                                     | 000110                                     |  |  |

| D09.y                    | 01001                      | 100                                        | 101                                        |  |  |

| D10.y                    | 01010                      | 010101                                     |                                            |  |  |

| D11.y                    | 01011                      | 110100                                     |                                            |  |  |

| D12.y                    | 01100                      | 001101                                     |                                            |  |  |

| D13.y                    | 01101                      | 101100                                     |                                            |  |  |

| D14.y                    | 01110                      | 011                                        | 100                                        |  |  |

| D15.y                    | 01111                      | 010111                                     | 101000                                     |  |  |

| D16.y                    | 10000                      | 011011                                     | 100100                                     |  |  |

| D17.y                    | 10001                      | 100                                        | 011                                        |  |  |

| D18.y                    | 10010                      | 010                                        | 011                                        |  |  |

| D19.y                    | 10011                      | 110                                        | 010                                        |  |  |

| D20.y                    | 10100                      | 001                                        | 011                                        |  |  |

| D21.y                    | 10101                      | 101                                        | 010                                        |  |  |

| D22.y                    | 10110                      |                                            | 010                                        |  |  |

| D/K23.y                  | 10111                      | 111010                                     | 000101                                     |  |  |

| D24.y                    | 11000                      | 110011                                     | 001100                                     |  |  |

| D25.y                    | 11001                      |                                            | 110                                        |  |  |

| D26.y                    | 11010                      | 010110                                     |                                            |  |  |

| D/K27.y                  | 11011                      | 110110 001001                              |                                            |  |  |

| D28.y                    | 11100                      | 001110                                     |                                            |  |  |

| K28.y                    | 11100                      | 001111 110000                              |                                            |  |  |

| D/K29.y                  | 11101                      | 101110                                     | 010001                                     |  |  |

| D/K30.y                  | 11110                      | 011110                                     | 100001                                     |  |  |

| D31.y                    | 11111                      | 101011 010100                              |                                            |  |  |

| Table 3-2 3B/4B Encoding          |     |                             |                             |  |  |  |

|-----------------------------------|-----|-----------------------------|-----------------------------|--|--|--|

| Input Output                      |     |                             |                             |  |  |  |

| Data Input Data bits 765<br>(HGF) |     | 5B/6B Disparity -ve<br>fghj | 5B/6B Disparity +ve<br>fghj |  |  |  |

| D/Kxx.0                           | 000 | 1011                        | 0100                        |  |  |  |

| Dxx.1                             | 001 | 100                         | )1                          |  |  |  |

| Kxx.1                             | 001 | 0110 1001                   |                             |  |  |  |

| Dxx.2                             | 010 | 0101                        |                             |  |  |  |

| Kxx.2                             | 010 | 1010                        | 0101                        |  |  |  |

| D/Kxx.3                           | 011 | 1100                        | 0011                        |  |  |  |

| D/Kxx.4                           | 100 | 1101                        | 0010                        |  |  |  |

| Dxx.5                             | 101 | 101                         | 10                          |  |  |  |

| Kxx.5                             | 101 | 0101 1010                   |                             |  |  |  |

| Dxx.6                             | 110 | 0110                        |                             |  |  |  |

| Kxx.6                             | 110 | 1001 0110                   |                             |  |  |  |

| Dxx.7                             | 111 | 1110/0111                   | 0001/1000                   |  |  |  |

| Kxx.7                             | 111 | 0111                        | 1000                        |  |  |  |

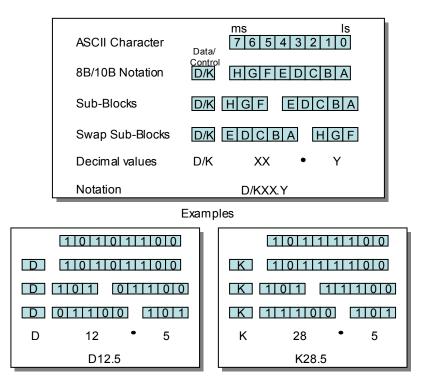

The 5B/6B and 3B/4B approach to 8B/10B encoding has lead to a specific notation for representing codes resulting from this encoding. This is illustrated in Figure 3-3.

The 12 control characters are listed in Table 3-3. Three of these characters (K28.1, K28.5 and K28.7) contain a unique seven bit pattern (0011111 or 1100000) which does not occur in any of the data

codes and which cannot be produced by concatenating any other two data or control codes. This pattern is known as the "comma" pattern and is widely used for performing receive code synchronisation (character alignment). The comma pattern is underlined in Table 3-3.

Note that K28.7 followed by certain other data or control codes can produce a false comma, but the correct one comes first.

| Table 3-3 8B/10B Control (K) Codes |                               |                               |  |  |  |

|------------------------------------|-------------------------------|-------------------------------|--|--|--|

| Input                              | Output                        |                               |  |  |  |

| Special Character Name             | Current Running Disparity -ve | Current Running Disparity +ve |  |  |  |

| K28.0                              | 001111 0100                   | 110000 1011                   |  |  |  |

| K28.1                              | <u>001111 1</u> 001           | <u>110000 0</u> 110           |  |  |  |

| K28.2                              | 001111 0101                   | 110000 1010                   |  |  |  |

| K28.3                              | 001111 0011                   | 110000 1100                   |  |  |  |

| K28.4                              | 001111 0010                   | 110000 1101                   |  |  |  |

| K28.5                              | <u>001111 1</u> 010           | <u>110000 0</u> 101           |  |  |  |

| K28.6                              | 001111 0110                   | 110000 1001                   |  |  |  |

| K28.7                              | <u>001111 1</u> 000           | <u>110000 0</u> 111           |  |  |  |

| K23.7                              | 111010 1000                   | 000101 0111                   |  |  |  |

| K27.7                              | 110110 1000                   | 001001 0111                   |  |  |  |

| K29.7                              | 101110 1000                   | 010001 0111                   |  |  |  |

| K30.7                              | 011110 1000                   | 100001 0111                   |  |  |  |

The initial disparity can be either positive or negative. The current running disparity of the 8B/10B decoder must always reflect the disparity of the most recently decoded input. This may cause a disparity error to be generated for the first character in a data stream but then the transmitter and receiver will become synchronised. This assumes that the data stream begins with at least one character which has two possible 8B/10B codings based on the current disparity.

Table 3-4 and Table 3-5 show how errors can be captured by monitoring for invalid codes and disparity errors. In Table 3-4 a single bit error converts the D00.0 character sent into a code whose 4B component does not appear in the 3B/4B coding table. This is immediately detected as a coding error.

| Table 3-4 Detection of error by invalid code |             |     |      |     |          |     |               |         |

|----------------------------------------------|-------------|-----|------|-----|----------|-----|---------------|---------|

| Character                                    | Transmitted |     |      |     | Received |     |               |         |

| D00.0                                        | 100111      | -ve | 0100 | -ve | 100111   | -ve | 0 <u>0</u> 00 | invalid |

In Table 3-5 an error occurs in the first line with the D08.1 character being changed to the D05.1 character. D05.1 is a valid character so goes undetected. The running disparity should however be positive but because of the error it is negative. The characters that follow have neutral disparity so the running disparity remains unchanged and no error is detected. Eventually a character, D15.1, is sent which does not have neutral disparity. At the transmitter the running disparity is negative prior to D15.1 so that character is encoded as 101000 1001 which has negative disparity. When this is received at the receiver the negative disparity causes an error because the running disparity there is already negative. The error has been caught by disparity but several characters were sent before the error because apparent.

The receiver should look out for both invalid characters and disparity errors. It is also important that a CRC code is added to each packet sent to ensure that any error in a packet is detected.

| Table 3-5 Detection of error by invalid disparity |             |     |      |     |                 |       |      |     |           |

|---------------------------------------------------|-------------|-----|------|-----|-----------------|-------|------|-----|-----------|

| Character                                         | Transmitted |     |      |     | Received        |       |      |     | Character |

| D08.1                                             | 111001      | +ve | 1001 | +ve | 1 <u>0</u> 1001 | -ve   | 1001 | -ve | D05.1     |

| D09.1                                             | 100101      | +ve | 1001 | +ve | 100101          | -ve   | 1001 | -ve | D09.1     |

| D10.1                                             | 010101      | +ve | 1001 | +ve | 010101          | -ve   | 1001 | -ve | D10.1     |

| D11.1                                             | 110100      | +ve | 1001 | +ve | 110100          | -ve   | 1001 | -ve | D11.1     |

| D12.1                                             | 001101      | +ve | 1001 | +ve | 001101          | -ve   | 1001 | -ve | D12.1     |

| D13.1                                             | 101100      | +ve | 1001 | +ve | 101100          | -ve   | 1001 | -ve | D13.1     |

| D14.1                                             | 011100      | +ve | 1001 | +ve | 011100          | -ve   | 1001 | -ve | D14.1     |

| D15.1                                             | 101000      | -ve | 1001 | -ve | 101000          | ERROR |      |     | D15.1     |

Page: 28 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

### 3.3 SERIALISATION AND DE-SERIALISATION

Serialisation is the conversion of a parallel data stream into a serial one. This is straightforward. The parallel 10-bit data word is loaded into a shift register and then shifted out using a transmit clock signal to drive the shift register. A new character has to be loaded into the parallel input of the shift register as soon as the previous 10-bit character has been shifted out to prevent a gap in the serial data.

De-serialisation is the opposite of serialisation. The serial data is shifted into a shift register using a receive clock (also called a bit clock). Recovery of the receive clock from the transmitted serial data stream is described in section 3.4 Once a full 10-bit character has been shifted into the shift register it is read out in parallel. The 10-bit character must be read out at the correct point in the serial data stream *i.e.* when a complete new 10-bit character is in the shift register. Character synchronisation is described in section 3.5.

## 3.4 RECEIVE CLOCK RECOVERY

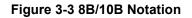

Recovery of the receive clock (bit clock) from the received serial data stream is done using a phaselocked loop (PLL). A typical phase-locked loop is shown in Figure 3-4

Figure 3-4 Typical Phase-Locked Loop

The phase of the incoming data stream is compared to the phase of a reference clock signal. The detected phase difference is filtered, removing noise and providing an average phase difference. The filtered phase difference is used to control the frequency of the reference clock. If there is a positive phase difference with edges in the data stream occurring before edges in the reference clock then the reference clock frequency must be increased so that it catches up with the data stream edges. If there is a negative phase difference then the reference clock is occurring too early so must be slowed down, in which case the reference clock frequency is reduced.

When locked so that there is no phase difference, the reference clock can be used to recover the data-bits from the serial stream.

High frequency phase locked loops are normally implemented using a voltage controlled oscillator and an analogue loop filter. Since the PLL is analogue it will not be defined in VHDL.

The time taken for a PLL to lock onto a signal is dependent upon the design of the PLL and the difference between the input bit stream phase and the PLL reference clock phase. Typically it takes at least 5000 edges in the bit stream for a PLL to lock although it can be substantially longer for some PLL designs.

#### 3.5 CHARACTER SYNCHRONISATION

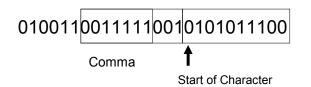

Character synchronisation is necessary in the receiver to separate out each character from the received bit stream. To do this is it necessary to identify where a character starts, after that each individual character can be separated by simply counting 10-bits for each character. Identifying the start of a character is used using the 8B/10B Comma bit sequences. Comma sequences are unique seven bit sequences:

- Plus Comma 0011111

- Negative Comma 1100000

An illustration of character synchronisation using a plus comma is shown in Figure 3-5. The start of the next character occurs on the fourth bit after the end of the detected plus comma.

#### Figure 3-5 Character Synchronisation Using a Plus Comma

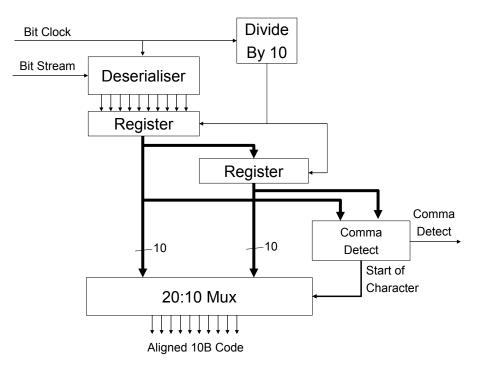

There are two principal means of performing character synchronisation. The first method, shown in Figure 3-6, performs the character synchronisation after de-serialisation, while the second method, illustrated in Figure 3-7, does it during de-serialisation.

Figure 3-6 shows the received bit stream being fed into the de-serialising shift register. As soon as ten bits have been received the de-serialised data is loaded into a register. The exact position of the ten bits in the data stream is not important. After a further ten bits have been received the data in the register is loaded into a second register and the de-serialised data is loaded into the first register. The

Page: 30 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

20 bits in these two registers are examined for a possible comma, using the comma detect circuitry. The combinatorial logic in the comma detect circuitry outputs a Comma Detect signal when a comma is found and registers the position of the start of the next character. The Start of Character is used to drive a 20:10 multiplexer which select the ten-bits of a character from the 20-bits in the two registers.

With this approach comma detection is done at a clock rate of one tenth of that of the bit stream. The comma detect circuitry has to simultaneously look for a comma in ten possible bit positions, requiring 10 correlators.

#### Figure 3-6 Character Alignment After De-serialisation

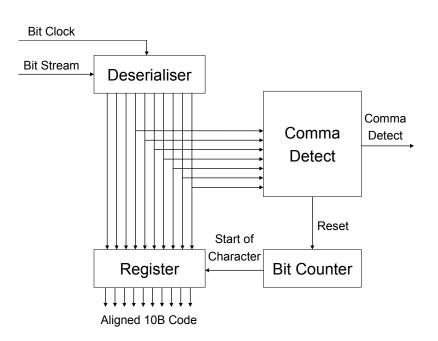

The other approach, performs comma detection at the bit clock rate. The bit stream is fed into a 10-bit shift register (de-serialiser). The 10-bit parallel output from the shift register fed to a 10-bit character register and to a Comma Detect circuit. The Comma Detect circuit looks for a Comma in the last seven bits of the shift register (*i.e.* the first seven bits to enter the shift register). When a comma is detected the data in the shift register are loaded into the data register. A bit counter is used to count the 10-bits in each character, loading the data register from the shift register every 10 bits. The comma detect circuit resets the counter, re-synchronising the bit counter and forcing the data in the shift register to be loaded into the data register.

This approach requires the comma detect circuitry to operate at the rate of the bit clock and needs a high-speed bit counter. The amount of circuitry is significantly less that the other approach.

Page: 31 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 3-7 Character Alignment During De-serialisation

#### 3.6 RECEIVE ELASTIC BUFFER

The two ends of a link are both expected to operate at the same frequency. In practice, however, there will be slight differences in the clocks at the two ends of the link. This can cause receive buffer overflow or under-run problems unless the difference in the two clock speeds is compensated for. This is achieved using a Receive Elastic Buffer and associated SKIP characters.

The receive clock (bit clock) is recovered from the incoming bit stream, so is at the same frequency as the transmit clock at the other end of the link. After de-serialisation and character synchronisation the incoming data must be transferred from the receive clock domain to the local system clock domain. In passing between these two clock domains, slight differences in the clock frequencies must be accommodated. This is achieved using the Receive Elastic Buffer.

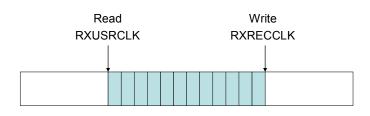

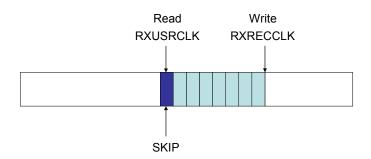

The normal situation with a Receive Elastic Buffer is illustrated in Figure 3-8. Data is written into the buffer using a write pointer which operates at the receive character rate (RXRECCLK). It is read out by read pointer which operates at the user system character rate (RXUSRCLK).

Page: 32 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

Nominal condition buffer half-full

#### Figure 3-8 Receive Elastic Buffer - Nominal Condition

Any difference between the two clock frequencies is compensated for using a special character, SKIP, inserted every so often into the data stream

If the RXUSRCLK is faster than RXRECCLK the buffer will slowly empty. When the buffer is less than half full, implying that RXUSRCLK is faster than RXRECCLK, extra SKIP characters are added to the Receive Elastic Buffer. This may be done when a SKIP character is read out of the buffer, by simply not incrementing the read pointer, so that the SKIP character will be read a second time. The effect is to add an extra SKIP character to the data stream, temporarily slowing down the RXUSRCLK to compensate for it being faster than RXRECCLK. This is illustrated in Figure 3-9.

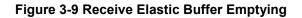

If RXUSRCLK is slower than RXRECCLK then the Receive Elastic Buffer will slowly fill up. When buffer more than half full, SKIP characters are skipped. This is done by incrementing the read pointer past a SKIP character, *i.e.* if after reading a character, the next character to be read is a SKIP character, it is ignored and the read pointer is moved to point to the following character instead. The effect is to remove SKIP characters from the buffer, temporarily speeding up the RXUSRCLK to make up for the fact that it is slower than RXRECCLK. This is shown in Figure 3-10. Note that the SKIP operation requires the elastic buffer to know in advance that a SKIP is present in the buffer without reading it otherwise the SKIP operation will have no effect.

Page: 33 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### **Outline Specification**

#### Figure 3-10 Receive Elastic Buffer Filling Up

For the Receive Elastic Buffer to work properly there must be sufficient SKIPs in the data stream, so that they can be remove if necessary. The frequency of SKIPs depends on the size of the elastic buffer and the maximum frequency difference between RXUSRCLK and RXRECCLK.

Assume that the nominal operational frequency is F characters per second and that the maximum clock difference, is D Hz, then the time, T, taken for the elastic buffer to have one character too many or one character too few is given by:

T = 1 / (Receive Clock Frequency – User Clock Frequency)

T = 1/((F+D) - (F-D)) = 1/(2D)

In this time the number of characters sent is

N = (F+D).T

which is approximately

N ≈ F/(2D)

since F is much greater than D.

Now D/F is the maximum clock drift, so

N ≈ 1/(2P)

Where P is the maximum drift in the clock.

For a  $\pm 100$  ppm maximum clock drift, which is readily achievable using crystal oscillators, D, is  $10^{-4}$ , and the number of characters sent before the elastic buffer is one character out is 5000. A SKIP character must thus be sent every 5000 characters to prevent the Elastic buffer from ever being more than one character out. This is the case independent of the size of the characters.

SKIPs will be inserted in pairs and they will be defined such that the comma at the start of one SKIP will be a positive comma while the one at the start of the other skip will be a negative comma. This is to allow devices that recognise only one type of comma to function correctly.

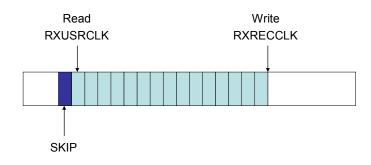

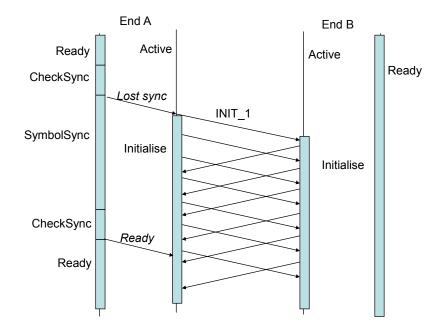

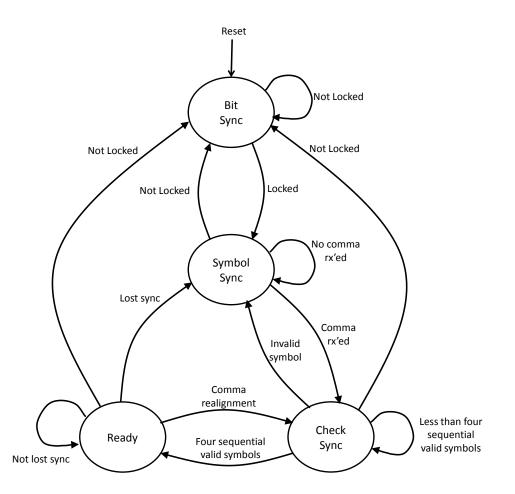

### 3.7 RECEIVE SYNCHRONISATION STATE MACHINE

The Receive Synchronisation state machine is used to determine and indicate when incoming data is properly synchronised at the bit and symbol level.

Bit synchronisation occurs once the receive clock recovery circuit has locked on to the bit transitions in the receive serial bit stream. If receive clock recovery is done with a PLL then bit synchronisation occurs when the PLL is locked or has been locked for a specified period of time.

Loss of bit synchronisation occurs when the receive clock recovery circuit losses lock to the bit transitions in the receive serial bit stream.

Symbol synchronisation occurs once symbols can be distinguished in the received serial data. Symbol boundaries can be identified using the unique comma sequence. One a comma code has been detected symbol synchronisation has occurred. To avoid incorrect symbol synchronisation due to noise it is prudent to confirm that valid symbols are being received after a comma sequence has been received. If this is that case then the receiver is synchronised and ready.

A loss of symbol synchronisation occurs when several invalid symbols have been received. A single symbol in error may mean that a transitory error occurred without losing synchronisation. A counter is used to count the number of invalid symbols. This counter is incremented by INVALID\_INCR (e.g. four) every time an invalid symbol is received, and is decremented by one every time a valid symbol is received. Assuming that just one invalid symbol is received, followed by many valid symbols, *i.e.* there is a transitory error, the INVALID\_INCR value determines how many valid symbols must be received before the arrival of the invalid symbol is completely forgotten. For example, if RX\_LOS\_INVALID\_INCR is four then when an invalid symbol arrives, the counter is incremented to four. Each subsequent valid symbol decrements this counter by one until it reaches zero, at which point the invalid symbol has been forgotten. If several invalid symbols arrive then the counter may reach a LOS\_THRESHOLD value in which case loss of synchronisation is triggered. Continuing the previous example, if LOS\_THRESHOLD is set to 12 it will take 3 successive invalid symbols to trigger loss of synchronisation, or 4 invalid symbols with one valid symbol between each of them.

The Receive Synchronisation state machine is illustrated in Figure 3-11.

**Outline Specification**

Page: 35 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 3-11 Receive Synchronisation State Machine

There are four states:

- BitSync the receiver is waiting for bit synchronisation to be achieved:

- Waits until the receive clock recovery circuit indicates that bit synchronisation has been achieved and then moves to the SymbolSync state.

- SymbolSync the receiver is in the process of symbol synchronisation:

- Waits for a Comma to be detected.

- When a Comma is received the next state is CheckSync.

- If the receive clock recovery circuitry indicates that bit synchronisation has been lost then the next state is BitSync.

- CheckSync the receiver is checking that proper symbol synchronisation has been achieved:

- Waits for four consecutive valid symbols.

- When four consecutive valid symbols have been received synchronisation has been acquired and the state machine moves to the Ready state.

- If an invalid symbol is received then symbol synchronisation has not been acquired so the state machine moves back to the SymbolSync state.

- If the receive clock recovery circuitry indicates that bit synchronisation has been lost then the next state is BitSync.

- Ready the receiver is synchronised:

- The counter is decremented by one for each valid symbol received.

- The counter cannot be decremented below zero.

- The counter is incremented by INVALID\_INCR for each invalid symbol.

- If the counter exceeds the LOS\_THRESHOLD value then the next state is the SymbolSync state.

- If a Comma realignment is detected it implies a change in the character synchronisation. resynchronisation is necessary so the next state is CheckSync.

- If the receive clock recovery circuitry indicates that bit synchronisation has been lost then the next state is BitSync.

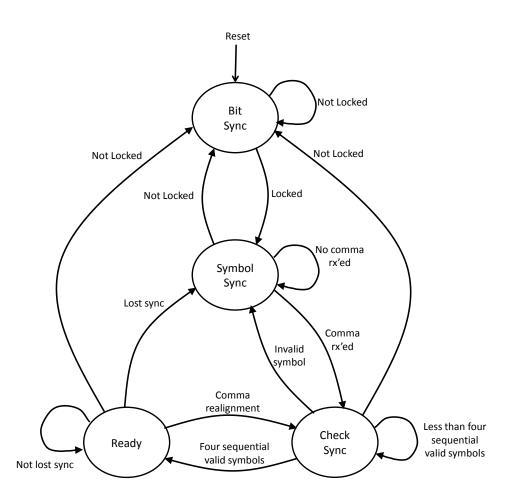

#### 3.8 LINK STATE MACHINE

The link state machine is responsible for getting the link up and running and for recovering from any errors. The same state machine will also be responsible for power management and for unidirectional link operation but this is beyond the scope of the current study.

Page: 37 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

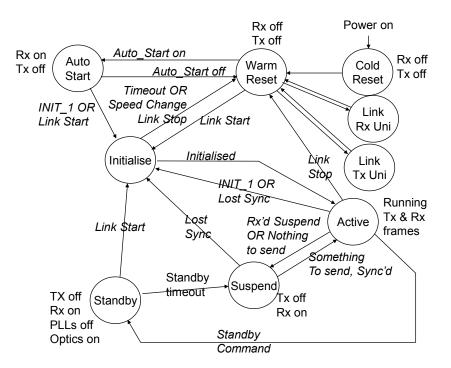

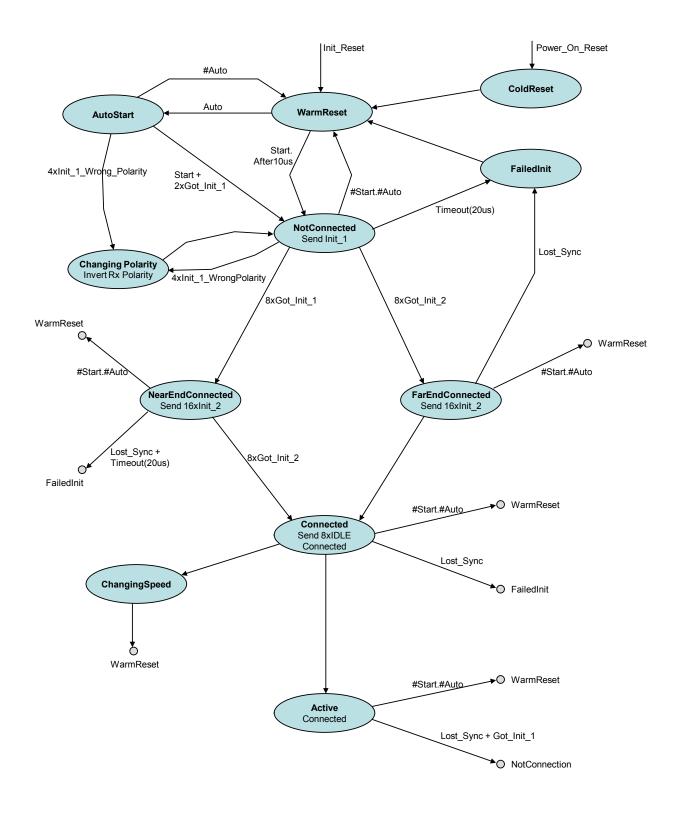

The Link state machine is illustrated in Figure 3-12.

Figure 3-12 Link State Machine

There are five principal states: cold reset, warm reset, auto-start, initialise and active. In addition there are two, or possibly more, power states: suspend and standby, and two states used to support unidirectional link operation: Link Tx Uni and Link Rx Uni. Only the five principal states are considered in this document.

The cold reset state is entered on powering up the link interface. In the cold reset state all link temporary registers and configuration registers are reset to their default values. After cold reset is complete the initialisation state machine moves to the warm reset state.

In the warm reset state the link temporary registers are reset to their default values. The link waits for a command from the local user application (host system). When an auto-start or link start command is give, by setting the auto-start bit or link start bit in a configuration register, the link state machine moves to the AutoStart state or Initialise state, respectively. In both the cold reset and the warm reset state both the receiver and transmitter are disabled.

In the AutoStart state the receiver is enabled to receive data. In this state the link state machine is waiting to receive data. When data is received and the receiver locks on to the received bit and symbol stream the link state machine moves to the Link Start state. If the link start command (link start bit set) is given then the link state machine moves immediately to the Link Start state without waiting

for data to be received first. If incorrect polarity of the input stream is detected then the polarity of the receiver may be inverted once.

In the Initialisation state the transmitter starts to send and listen for INIT\_1 and INIT\_2 ordered sets as part of the initialisation handshake. This is described later in Section 3.9. When the initialisation handshake is complete the link state machine moves to the Active state. If there is an initialisation timeout or the link is stopped (Start and Auto Start off) while in the Initialisation state then the link state machine moves back to the warm reset state. If incorrect polarity of the input stream is detected then the polarity of the receiver may be inverted once.

In the Active state the link can send and receive user ordered sets and data frames. If there is a persistent error and synchronisation is lost then the link state machine returns to the Initialisation state. If it receives an INIT\_1 ordered set while in the Active state this indicates that the other end of the link has lost synchronisation: the state machine moves to the Initialisation state and the link is re-initialised to attempt to recover from the error. If the link is stopped (Link Start and Auto Start are both disabled) then the link state machine moves to the warm reset state.

Note that a receiver polarity correction may be made at most once after leaving warm reset until the state machine returns to warm reset (directly or indirectly via a cold reset).

# 3.9 LINK INITIALISATION

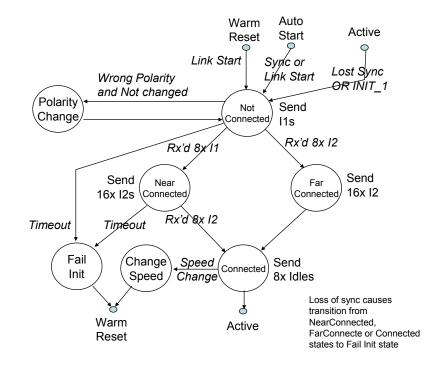

The Link Initialisation state comprises several sub-states which are illustrated in Figure 3-13.

Page: 39 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 3-13 Link Initialisation State Machine

The Link Initialisation state machine achieves a connection using a simple bi-directional handshake. INIT\_1 ordered sets are transmitted by the near end. When the far end has synchronised and received eight consecutive INIT\_1s it acknowledges this by sending INIT\_2. Receiving INIT\_1s allows the link interface to synchronise. Receiving INIT\_2s indicates that the far end has synchronised.

There are four main states in the Link Initialisation state machine which are named according to the knowledge about the near end and far end of the link. If the near end has synchronised properly and received some INIT\_1 initialisation ordered sets then it can be considered as being connected, prior to this it is not connected. The receipt of INIT\_2 initialisation ordered sets indicates that the far end has received initialisation ordered sets, synchronised and become connected. The four primary states are:

- NotConnected: Near end not connected, far end not connected. This is the situation before either end has synchronised and become connected.

- NearConnected: Near end connected, far end not connected. This is the situation when the near end has synchronised on the incoming INIT\_1 ordered sets and received 8 consecutive INIT\_1s.

- FarConnected: Near end not connected, far end connected. The far end has synchronised first, before the near end. Having achieved synchronisation the far end has started to send INIT\_2s which have been received at the near end. In fact both ends are synchronised but the near end synchronisation has to be signalled by sending INIT\_2s to the far end.

- Connected: Near end connected, far end connected. Both the near end and far end have synchronised successfully so the link is ready to transfer data.

The NotConnected state is entered from the warm reset state when the link start bit is set, from the auto-start state when an INIT\_1 has been received or when the link start bit is set, or from the Active state when receiver synchronisation is lost (lost\_sync) or an INIT\_1 ordered set is received, indicating that the receiver at the far end of the link has lost synchronisation. In this state the link interface transmits INIT\_1 ordered sets so that the far end of the link can synchronise. If the far end of the link is also in the NotConnected state then it will also be sending INIT\_1s they will be received by the near end receiver causing it to synchronise and star receiving the INIT\_1 ordered sets. When the receiver has received eight consecutive INIT\_1s the link initialisation state machine moves to the NearConnected state. If it receives eight consecutive INIT\_2s before it receives eight consecutive INIT\_1s then the far end has made a connection before the near end so the state machine moves to the FarConnected state. A timeout timer is started on entering the NotConnected state, if this timeout timer expires then the link has failed to initialise and the state machine moves to the Fail Init state.

Page: 40 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

The NearConnected state is entered from the NotConnected state when the receiver has received eight consecutive INIT\_1s. This means that the near end has correctly synchronised. It signals this condition back to the far end of the link by sending INIT\_2s. IN the NearConnected state when eight consecutive INIT\_2s have been received it means that the far end has synchronised successfully so the link initialisation state machine moves to the Connected state. A timeout timer is started on entering the NearConnected state, if this timeout timer expires then the link has failed to initialise and the state machine moves to the Fail Init state.

The FarConnected state is entered from the NotConnected state when the receiver has received eight consecutive INIT\_2s. This indicates that the far end of the link has initialised quickly before the near end has synchronised and received eight INIT\_1s. In the FarConnected state communication in both directions has been established. It only remains to signal the fact that the near end has synchronised to the far end. It does this by sending 16 INIT\_2s on the assumption that since both ends of the link are synchronised eight of these INIT\_2s will be received consecutively by the far end. As soon as the 16 INIT\_2s have been sent the link initialisation state machine moves unconditionally to the Connected state.

In the Connected state the link is synchronised in both directions. To allow both ends to finish sending any outstanding INIT\_2s eight IDLE ordered sets are transmitted and then the link state machine moves to the Active state. In the Connected state if a speed change is required then the link initialisation state machine moves to the Speed Change state rather than the Active state.

In addition to the four states primary states there are three secondary states:

- Polarity Change: This state is entered if the polarity of the receiver input is found to be inverted. The polarity of the receiver is inverted to compensate for this and the state machine reverts back to the NotConnected state to complete initialisation. The polarity may not be changed more than once without passing through warm reset. Note that if the polarity was changed while in auto-start then it may not be changed again when in any of these states unless the warm-reset state has been visited first.

- Speed Change: The INIT\_1 and INIT\_2 ordered sets contain information about the maximum operating rate of the end of the link that sent those ordered sets. The speed change state is entered after initialisation is complete if it is determined that both end of the link are capable of operating at a higher rate than the current operating rate. The link speed is set to the maximum rate that both ends of the link can operate at and then the link state machine goes back to the warm reset and re-initialises at the new data rate.

- Fail Init: If the link fails to initialise then this state is entered. The cause of the failure can be recorded in a set of persistent registers (*i.e.* registers not cleared by warm reset). This information can then be used by higher layer software to determine what to do in the event o a

persistent failure. For example if the link continually fails to initialise at the highest common speed the link may be initialised at a lower operating speed.

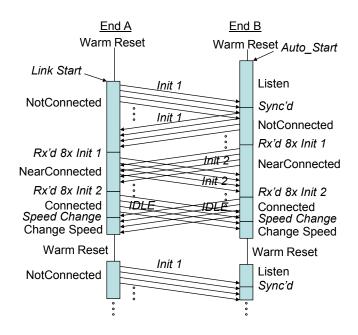

# 3.10 LINK INITIALISATION SEQUENCE DIAGRAMS

In this section several sequence diagrams are presented showing the operation of the link initialisation state machine under various conditions.

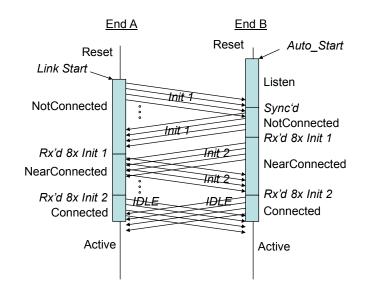

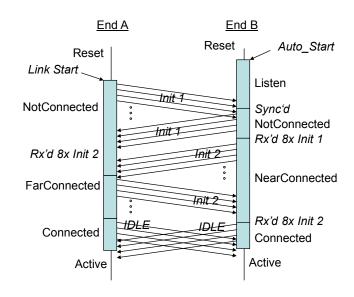

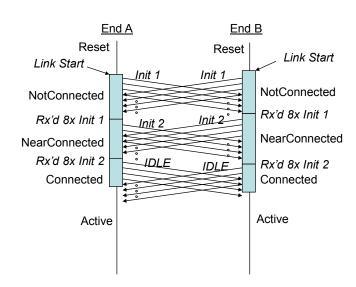

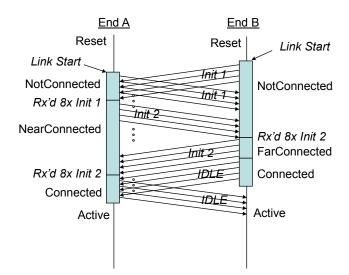

#### 3.10.1 Initialisation from AutoStart

Operation of the Link Initialisation state machine when one end (End B) is in the Auto-Start state and the other end (End A) has its link interface started (Link Start) is illustrated in the sequence diagram of Figure 3-14. In the sequence diagrams used in this document time goes from the top of the diagram to the bottom and the lines from top to bottom represent the life of a state machine. The narrow rectangles drawn on a state machine represent each state of the state machine with the name of the state being written adjacent to each rectangle (*e.g.* NotConnected). The events that cause transitions from one state to another are written in italics (*e.g.* Rx'd 8x Init 1). Arrows between the two link end state machines represent the transfer of relevant information between the two state machines, *i.e.* across the link, (*e.g.* Init 1). Arrows coming from the left-hand side of the diagram represent external events from the user application (host system) at End A (*e.g.* Link Start), while those from the right-hand side are from the user application at End B (*e.g.* Auto\_Start).

In Figure 3-14, End B is given an auto\_start command putting it into the Auto\_Start state, where it waits for a bit stream to start to come in on its receiver. End A is given a link start command and moves to the NotConnected state, where it starts sending INIT\_1s. These INIT\_1s are received at End B which synchronises to the bit stream and moves to the NotConnected state. End B now starts sending INIT\_1s. At least 16 INIT\_1s must be sent. These INIT\_1s are received at End A causing the receiver to synchronise. End B receives eight INIT\_1s and moves to the NearConnected state where it starts sending INIT\_2s to indicate to End A that it is synchronised. End A in the meantime has synchronised to the bit stream and received eight INIT\_1s. Both ends now start sending INIT\_2s. When each end has received eight INIT\_2s it moves to the Connected state, sends eight IDLEs and then moves to the Active state where it can send and receive data.

# SpaceFibre Outline Specification

Page: 42 / 89 Ref.: UoD\_SpFi\_Spec Issue: Draft A Date: 31-Oct-2007

#### Figure 3-14: Initialisation from Auto-Start