# Intellectual Property Macrocell for

# **SpaceWire Interface**

# **Compliant with AMBA-APB Bus**

L. Fanucci, A. Renieri, P. Terreni

Tel. +39 050 2217 668, Fax. +39 050 2217522

Email: luca.fanucci@iet.unipi.it

#### **Outline**

- Motivations of the work

- Reference SoC Platform

- SpaceWire Interface overview

- SpaceWire Encoder-Decoder

- AMBA<sup>TM</sup> APB interface

- Design and Verification Methodology

- Results and Conclusions

#### **Motivations of the Work**

ALY (1343)

CNR - Università di Pisa - ITALY

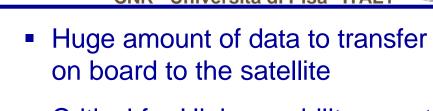

Forthcoming space applications demand:

more... but less...

- computational power

- mass, weight and power consumption

standardization

cost

reliability

development time

Candidate solutions are based on embedded systems, supporting standard and efficient communication protocols, developed by means of proper design and verification methodologies.

# **SpaceWire Standard**

CNR - Università di Pisa - ITALY

- Critical for High-capability remotesensing missions

- Cost, flexibility and reuse

- New serial data link standard, SpaceWire (ECSS-E-50-12A)

- Development of complex System On Chip (SoC)

SpaceWire Interface Intellectual Property (IP) macrocell

#### Reference SoC Architecture

Architecture

CNR - Università di Pisa - ITALY

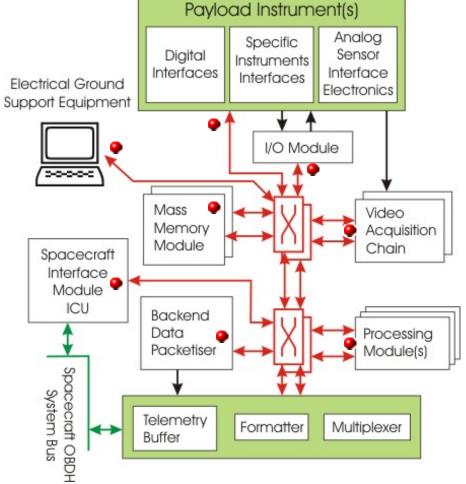

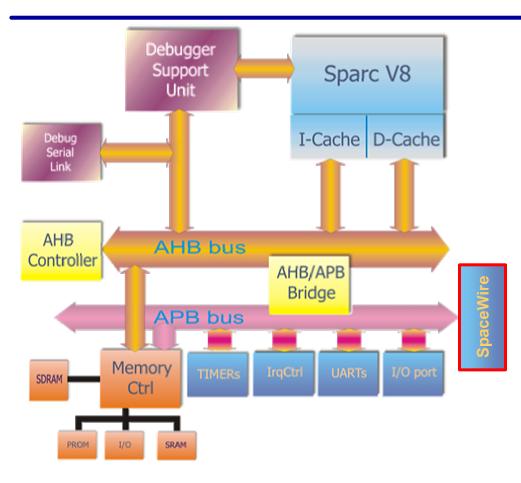

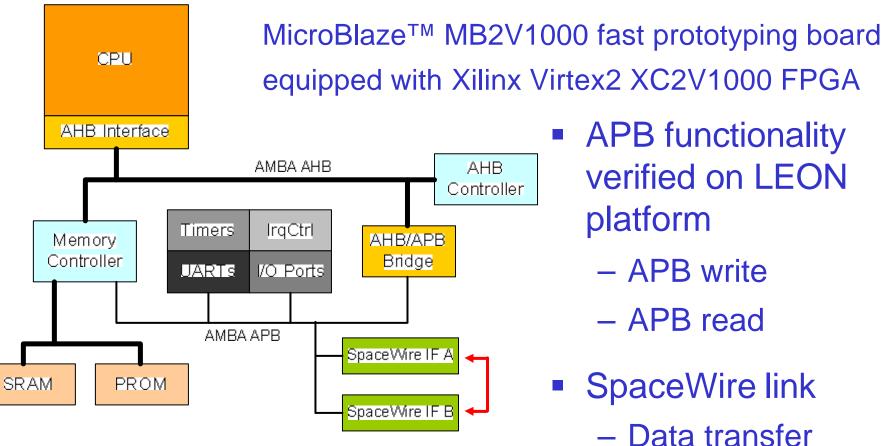

ESA LEON platform as reference SoC architecture

SpaceWire I/F AMBA™ APB bus compliant

SpaceWire interface IP suitable to any AMBA<sup>TM</sup> based SoC architecture

LEON platform site:

http://www.gaisler.com

ARM AMBA<sup>TM</sup> bus site: <a href="http://www.arm.com">http://www.arm.com</a>

#### **ESA LEON Embedded Core**

Dedded Core

CNR - Università di Pisa - ITALY

#### The LEON platform provides:

- SPARC-V8 compliant processor

- AMBA 2.0 bus core

- In-circuit debug interface

- General purpose peripherals

### Considered configuration

#### **Processor:**

- 32 Register windows

- 2K I-Cache and D-Cache

- Multiplier 16X16 (latency=4)

- MAC present

- No FPU neither coprocessor

#### Peripherals:

- Debug Support Unit present

- 32KB AHB RAM

- 2 UARTs + Parallel I/O port

- 1 Interrupt Controller

- 2 Timers + Watchdog

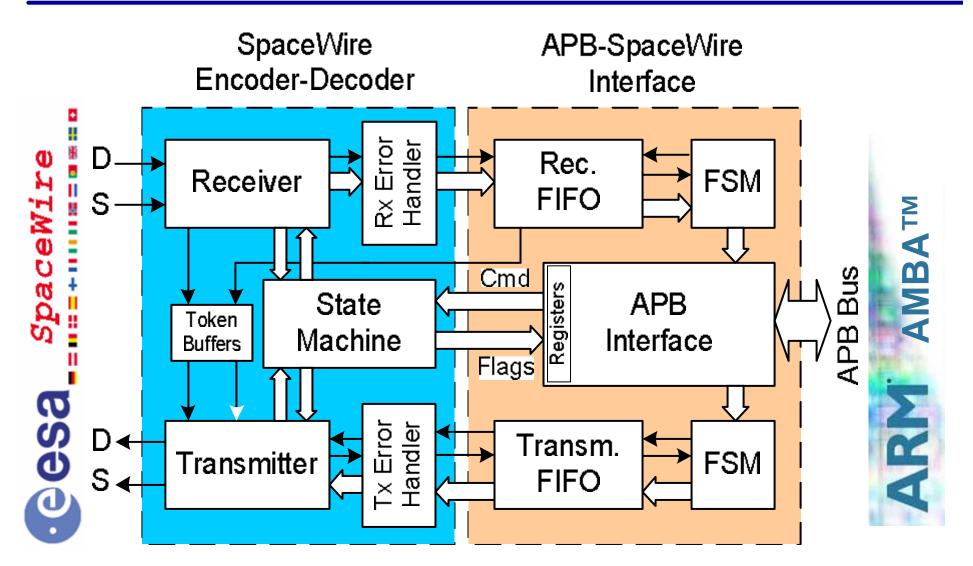

## **SpaceWire I/F for APB Bus**

LY (1313)

CNR - Università di Pisa - ITAL

# **Verification methodology**<sub>1/2</sub>

ALY (343)

CNR - Università di Pisa - ITALY

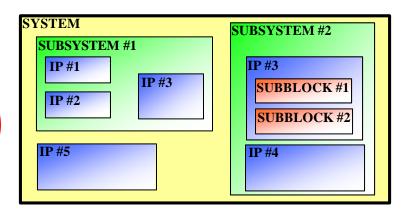

The more the system complexity grows, the bigger the effort required for the verification phase in order to guarantee the system reliability

A proper verification methodology needs to be adopted

Identify the correct hierarchy-level among:

- sub-block

- ·IP

- sub-system

- system

Identify the correct abstraction-level among architectural, (RTL) gate-level, layout

# **Verification methodology**<sub>2/2</sub>

CNR - Università di Pisa - ITAL)

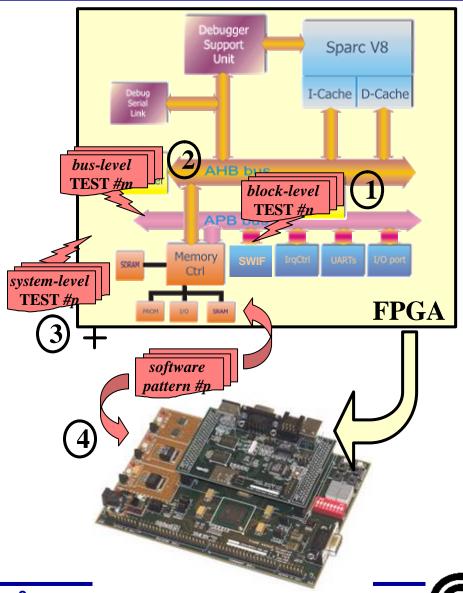

- block-level simulation: the IP is verified as stand alone

- 2) bus-level simulation: the IP is verified with IPs having the same functionality or sharing the same bus

- 3) system-level simulation: the IP is verified once it is plugged on the whole system. The verification is mainly performed via software patterns

- 4) hardware emulation: the system is mapped onto a fast-prototyping board and the software patterns developed in step 3) are used

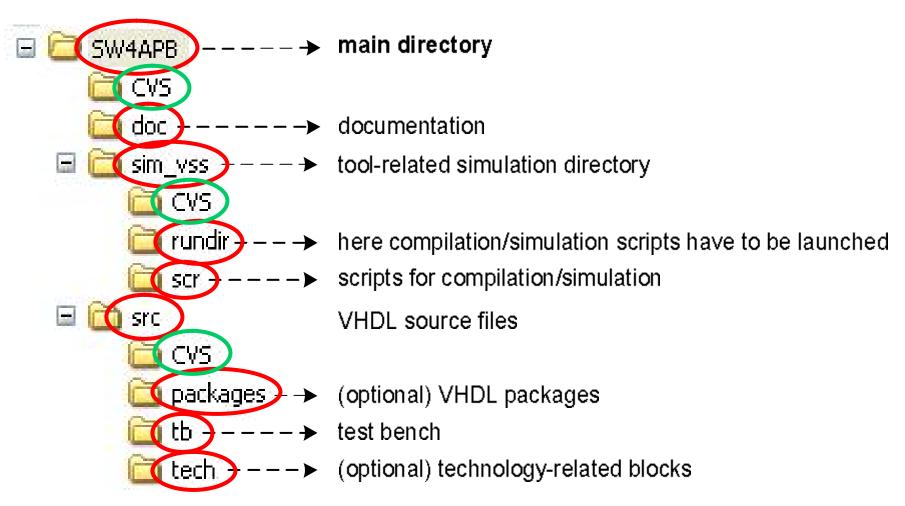

### **Database Structure**<sub>1/2</sub>

ALY (7343)

CNR - Università di Pisa - ITALY

Sources under CVS control (Concurrent Versions System)

# **Database Structure**<sub>2/2</sub>

LY (1343)

CNR - Università di Pisa - ITALY

### Well defined database structure leads to:

- ✓ Effective design and easy integration flow

- ✓ "Plug and Play" integration of IPs

- Reuse of scripts for top level integration

- ✓ Control over synthesis and simulation errors

- Top level script includes already verified lower level hierarchy scripts (IPs)

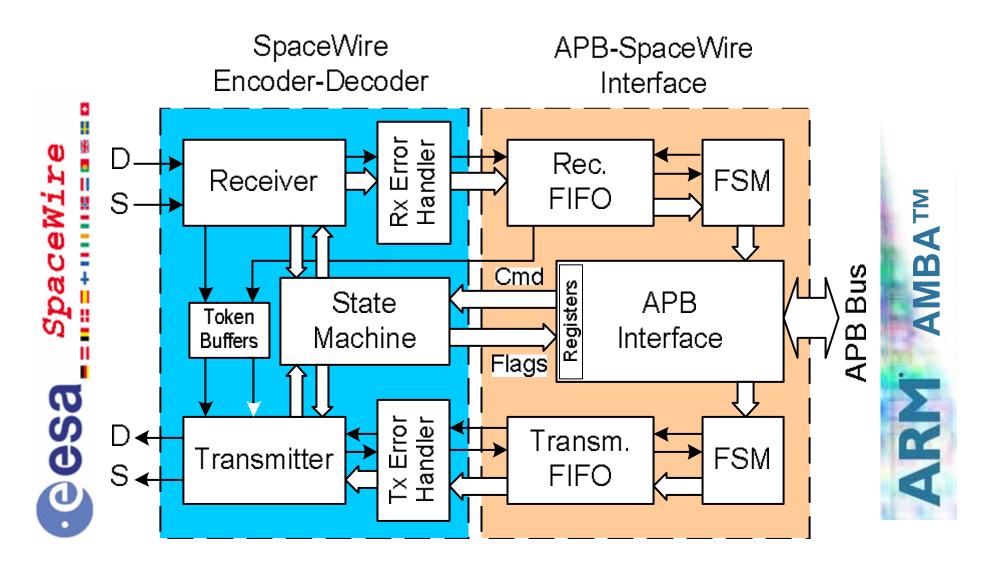

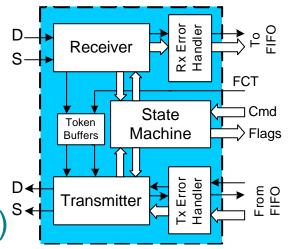

## **SpaceWire Interface**

ALY (1343s)

CNR - Università di Pisa - ITAL'

- ✓ Generic External Interface

- √ 3 clock domains

- Receiver (recovered from DS)

- Transmitter (derived from system clock)

- State Machine and timers (system clock)

- Token Buffers

- ✓ Error Handlers

- Tx: to spill partially transmitted packets

- Rx: to add EEP to partially received packets

- Extra signals to check the Status of the SpaceWire link

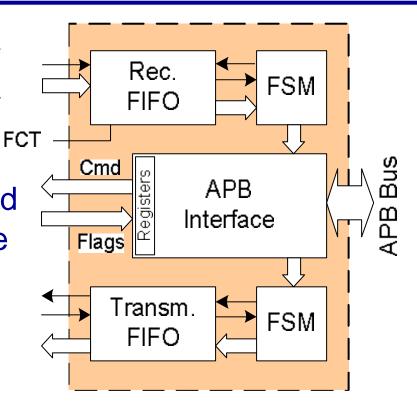

#### **APB Interface**

CNR - Università di Pisa - ITAL

✓ AMBA<sup>TM</sup> 2.0 Compliant Interface

✓ 2 asynchronous FIFO buffers for Receiver and Transmitter

✓ Status registers for command and status signals to/from SpaceWire interface

✓ Two Normal Characters moved concurrently on APB bus

| 31       | 30:25 | 24                               | 23:16       | 15       | 14:9 | 8                             | 7:0         |

|----------|-------|----------------------------------|-------------|----------|------|-------------------------------|-------------|

| DAV<br>2 | Res.  | Character 2<br>Data/Control flag | Character 2 | DAV<br>1 | Res. | Character 1 Data/Control flag | Character 1 |

DAV used in read operations only

# **Synthesis Results**

ALY (343)

CNR - Università di Pisa - ITAL

| Component       | Complexity   |               |  |  |  |

|-----------------|--------------|---------------|--|--|--|

|                 | Xilinx LUTs  | Equiv. Gates  |  |  |  |

| Encoder-Decoder | 275 LUTs     | 2 KGates      |  |  |  |

| APB Interface   | 202 LUTs     | \$31,5 KGates |  |  |  |

| Overall         | FKQH477 LUTS | QM 3.5 KGates |  |  |  |

Maximum Clock Speed on XILINX VIRTEX-II FPGA

120 MHz

## **Functionality Tests**

CNR - Università di Pisa - ITAL

equipped with Xilinx Virtex2 XC2V1000 FPGA

- APB functionality verified on LEON platform

- APB write

- APB read

- SpaceWire link

- Data transfer between two I/Fs

### Lack of a SpaceWire conformance test

#### **Conclusions**

ALY (343.5)

CNR - Università di Pisa - ITALY

- The use of a standardized SpaceWire link facilitates on-board connectivity with different equipment developed by different manufacturers

- Future SoCs for space applications call for an easily integrable

SpaceWire IP Macrocell

- A SpaceWire interface compliant with AMBA<sup>TM</sup> APB bus has been presented

- A proper design and verification methodology in conjunction with a well defined IP database structure has been set-up and used aiming to further improve overall system reliability

- The SpaceWire interface has been tested using a LEON-based SoC platform

- Further functional tests are on-going. (SpaceWire Conformance Tester?)